ILLIAC IV计算机

跳转到导航跳转搜索ILLIAC IV是第一台大规模并行计算机。[1]该系统最初设计为具有256个64位浮点单元(FPU)和4个能够每秒处理10亿次操作的中央处理单元(CPU)。[2]由于预算限制,仅建造了具有64个FPU和单CPU的单一象限。由于FPU都必须处理相同的指令-加法、减法等-在现代术语中,设计将被认为是单指令、多数据或SIMD。[3]。

1952年,丹尼尔·斯洛特尼克(Daniel Slotnick)在IAS机器上担任程序员时,产生了使用处理器阵列建造计算机的概念。正式的设计直到1960年才开始,当时斯洛特尼克在西屋电气工作,并根据美国空军的一份合同安排了开发资金。1964年,当这笔资金结束时,斯洛特尼克搬到了伊利诺伊大学,加入了伊利诺伊自动计算机(ILLIAC)团队。在高级研究计划局(ARPA)的资助下,他们开始了256个64位处理器的更新概念的设计,而不是原来的1024个1位处理器的概念。

在Burroughs建造这台机器的同时,这所大学开始建造一座新的设施来容纳它。美国国防部资助的政治紧张局势导致ARPA和大学担心这台机器的安全。当这台机器的第一个64处理器象限在1972年完工时,它被送到了加州的NASA艾姆斯研究中心。经过三年的彻底改装以修复各种缺陷,ILLIAC IV于1975年11月连接到ARPANet上进行分布式使用,成为第一台可联网的超级计算机,比Cray-1早了近12个月。

1象限的ILLIAC IV以其设计速度的一半运行,提供了50%的MFLOP峰值,[4]使其成为当时世界上最快的计算机。它还被认为是第一台使用固态存储器的大型计算机,也是迄今为止建造的最复杂的计算机,拥有100多万个门。[5]通常认为是由于大规模预算超支造成的失败,[5][6]该设计有助于开发用于编程并行系统的新技术和系统。在20世纪80年代,几台基于ILLIAC IV概念的机器成功交付。

1952年6月,丹尼尔·斯洛特尼克(Daniel Slotnick)开始在普林斯顿大学高级研究所(IAS)研究IAS机器。[7]IAS机器的特点是有一个对40位字进行运算的位并行数学单元。[8]最初配备威廉姆斯管存储器,后来增加了工程研究协会的磁鼓。该磁鼓有80个磁道,因此一次可以读取两个字,每个磁道存储1024位。[9]。

当思索鼓的机械装置时,斯洛特尼克开始怀疑这是否是制造计算机的正确方式。如果将字的位串行写入单个磁道,而不是并行写入40个磁道,则数据可以直接从磁鼓逐位送入位串行计算机。磁鼓仍将具有多个磁道和磁头,但在此概念中,每个磁道上的数据将被一次一位地读取并发送到并行ALU中,而不是聚集一个字并将其发送到单个ALU。这将是一台字并行、位串行的计算机。[7]。

斯洛特尼克在IAS上提出了这个想法,但约翰·冯·诺伊曼(John Von Neumann)以要求太多管子为由对其不屑一顾。[7]1954年2月,斯洛特尼克离开IAS回到学校攻读博士学位,这件事被遗忘了。[7]。

在完成博士和一些博士后工作后,斯洛特尼克最终在IBM工作。到这个时候,至少在科学计算方面,管和鼓已经被晶体管和核心存储器所取代。并行处理器处理来自同一鼓的不同数据流的想法不再具有同样明显的吸引力。然而,进一步的研究表明,并行机在某些应用中仍然可以提供显著的性能;Slotnick和他的同事John Cocke在1958年写了一篇关于这一概念的论文。[10]

在IBM和Aeronca飞机公司工作了一小段时间后,斯洛特尼克最终在西屋电气的空军部门工作,该部门从事雷达和类似系统的工作。[11]根据美国空军RADC的一份合同,斯洛特尼克能够组建一个团队,设计一个拥有1024个位串行ALU的系统,也就是众所周知的处理元件或PE。这个设计被命名为所罗门,以所罗门国王的名字命名,所罗门国王非常聪明,有1000名妻子。[12]。

PE将从单个主中央处理单元(CPU)、控制单元或CU获得指令。所罗门的CU会从内存中读取指令,对其进行解码,然后将其交给PE进行处理。每个PE都有自己的内存来保存操作数和结果,即PE内存模块或PEM。CU可以通过专用内存总线访问整个内存,而PE只能访问他们自己的PEM。[13]为了允许一个PE的结果用作另一个PE的输入,一个单独的网络将每个PE连接到其最接近的八个邻居。[14]。

建立了几个试验台系统,包括一个3×3(9个PE)系统和一个带有简化PE的10×10模型。在此期间,考虑了更复杂的PE设计,成为以256×32排列方式组织的24位并行系统。使用这种设计的单个PE建于1963年。随着设计工作的继续,美国国防部内的主要赞助商在一次事故中丧生,没有进一步的资金来源。[15]。

为了继续开发,斯洛特尼克接洽了利弗莫尔,当时利弗莫尔在购买超级计算机方面处于领先地位。他们对设计非常感兴趣,但说服他将目前设计的定点数学单元升级为真正的浮点,这导致了SOLOMON.2设计。[16]。

利弗莫尔不愿为开发提供资金,相反,他们提供了一份合同,一旦机器完成,他们将出租该机器。西屋电气管理层认为风险太大,于是关闭了团队。斯洛特尼克离开了西屋电气,试图寻找风险资本来继续该项目,但失败了。利弗莫尔后来选择了疾控中心的STAR-100担任这一角色,因为疾控中心愿意承担开发成本。[17]。

所罗门毕业后,斯洛特尼克加入了伊利诺伊大学厄巴纳-香槟分校的伊利诺伊自动计算机设计(ILLIAC)团队。伊利诺伊州自1949年以来一直为美国国防部和高级研究计划局(ARPA)设计和制造大型计算机。1964年,该大学与ARPA签署了一份合同,为这项工作提供资金,这项工作后来被称为ILLIAC IV,因为这是该大学设计和制造的第四台计算机。开发始于1965年,第一道设计于1966年完成。[18]。

与所罗门的位串行概念不同,在ILLIAC IV中,PE';被升级为全64位(位并行)处理器,使用12,000个门和2048个字的薄膜存储器。[19]PE有5个64位寄存器,每个寄存器都有特殊用途。其中一个,RGR,用于与相邻PE进行数据通信,每个时钟周期移动一个跳跃。另一个寄存器RGD指示该PE当前是否处于活动状态。非活动PE无法访问内存,但它们会使用RGR将结果传递给相邻PE。[14]PE被设计为作为单个64位FPU、两个32位半精度FPU或八个8位定点处理器工作。[19]。

新的设计没有1024个PE和一个CU,而是总共有256个PE排列成四个64个PE象限,每个象限都有自己的CU。CU';也是64位设计,有64个64位寄存器和另外4个64位累加器。该系统可以作为四台独立的64-PE机器、两台128-PE机器或一台256-PE机器运行。这允许系统在数据太小而无法要求整个256-PE阵列时处理不同的问题。[19]

基于25兆赫兹时钟,所有256-PE在单个程序上运行,该机器设计为每秒提供10亿次浮点运算,或者用今天的术语说,1兆GFLOPS。[20]这使得它比世界上任何一台机器都快得多;当代的CDC7600的时钟周期为27.5兆纳秒,或36兆秒/秒[21],尽管出于各种原因,它的性能通常接近10兆秒/秒。[22][a][a]。

为了支持这台机器,建造了数字计算机实验室大楼的扩建部分。[23]该大学的样本工作主要针对如何有效地向PE填充数据,从而进行计算机开发中的第一次压力测试。为了尽可能地简化这一点,创建了几种新的计算机语言;IVTRAN和TENAIL是FORTRAN的并行版本,Glypnir是ALGOL的类似转换。通常,这些语言支持跨并行执行的PE加载数据数组,有些语言甚至支持将循环展开为数组操作。[25]。

1966年初,该大学发出了一份征求建议书的请求,寻找有兴趣建造该设计的工业合作伙伴。7月份收到17份回复,其中7份回复,其中3份被选中。[26]一些回应,包括控制数据,试图让他们对矢量处理器设计感兴趣,但由于这些已经在设计中,团队对构建另一个不感兴趣。1966年8月,向RCA、Burroughs和Univac提供了为期8个月的合同,以投标建造该机器。[19]。

在与德州仪器(TI)合作后,Burroughs最终赢得了合同。这两家公司都提供了新的技术进步,使他们的竞标变得最有趣。Burroughs提出要制造一种新的、速度更快的薄膜存储器,这将提高性能。TI提出要建造64针发射极耦合逻辑(ECL)集成电路(IC),每个IC有20个逻辑门。[C]当时,大多数IC使用16针封装,有4到7个门。使用TI的IC将使系统变得更小。[19]。

Burroughs还提供了专门的磁盘驱动器,它为每个磁道配备了单独的固定磁头,可以提供高达500兆比特/秒的速度,每个36&34;磁盘存储约80MB。他们还将提供一台Burroughs B6500大型机作为前端控制器,从辅助存储加载数据并执行其他内务任务。连接到B6500的是第三方激光光学记录介质,这是一种一次写入系统,可在由旋转滚筒携带的聚酯片上涂覆的金属薄膜上存储高达1TBIT的数据。新设计的施工在Burroughs';Great Valley实验室开始。[13]当时估计这台机器将于1970年初交付。[27][27]。

在研究了一年的IC之后,TI宣布他们未能制造出64针的设计。更复杂的内部布线导致了电路中的串扰,他们要求再花一年的时间来解决问题。取而代之的是,ILLIAC团队选择基于可用的16针IC重新设计机器。这要求系统运行速度较慢,使用16兆赫的时钟,而不是原来的25兆赫。[28]从64针到16针的改变花费了该项目大约两年的时间和数百万美元。TI在又过了一年多一点的时间就能够让64针设计开始工作,并在ILLIAC完成之前开始在市场上提供它们。[28][28]。

由于这一变化,单个PC板的面积增加了约1英寸(2.5厘米),达到约6英寸乘10英寸(15厘米×625厘米)。这注定了Burroughs为这台机器生产薄膜存储器的努力失败了,因为现在已经没有足够的空间让存储器放进设计的橱柜里了。这一点注定了Burroughs为这台机器生产薄膜存储器的努力失败了,因为现在已经没有足够的空间让存储器放进设计的橱柜里了。试图增加机柜的大小来为存储器腾出空间,导致了信号传播的严重问题。[29]斯洛特尼克调查了潜在的替代品,并从飞兆半导体公司挑选了一款半导体存储器,这一决定遭到了巴罗斯的强烈反对,随后ARPA进行了全面审查。[19]。

1969年,这些问题,再加上延误造成的成本超支,导致决定只建造一个64个PE象限[19],从而将机器的速度限制在大约200MFLOPS。[30]这些变化总共花费了该项目三年时间和600万美元。[19]到1969年,该项目每月花费100万美元,不得不从最初的ILLIAC团队中剥离出来,他们越来越强烈地反对该项目。[31][31]

到1970年,这台机器终于以合理的速度建造起来,并准备在大约一年后交付。1970年1月6日,学生报纸“伊利尼日报”(Daily Illini)宣称,这台计算机将用于设计核武器。[32]5月,肯特州立大学发生枪击事件,大学校园爆发反战暴力事件。[31][31]。

斯洛特尼克逐渐反对在机密研究中使用这台机器,并宣布,只要是基于大学的理由,在机器上进行的所有处理都将被公开。他还越来越担心这台机器会受到更激进的学生团体的攻击。[31]这一立场在当地学生于1970年5月9日加入全国学生罢工的行列,宣布为伊利行动日,尤其是8月24日威斯康星大学麦迪逊分校数学大楼爆炸事件之后,似乎是明智的。[34]。

在后来成为硅谷的美国宇航局艾姆斯研究中心主任汉斯·马克的帮助下,1971年1月,决定将这台机器交付给艾姆斯,而不是这所大学。位于一个活跃的美国海军基地,由美国海军陆战队保护,安全将不再是一个令人担忧的问题。这台机器最终在1972年4月交付给埃姆斯,并安装在N-233大楼的中央计算机设施中。[35]到这一点上,已经晚了几年,而且远远超过了预算,总价为3100万美元,几乎是整个256-PE机器最初估计的800万美元的四倍。[31][2][d][e]。

NASA还决定用PDP-10取代B6500前置机,PDP-10是Ames常用的,将使其更容易连接到ARPAnet。[36]这需要在PDP-10上开发新的软件,特别是编译器。这导致了机器上线的进一步延迟。[31][31]。

ILLIAC IV由哈罗德·范·阿内姆(Harold Van Arnem)领导的ACTS计算公司根据与国防部签订的成本加成合同进行管理。梅尔·皮特尔博士拥有伯克利大学和伯克利计算机公司(BCC)的背景,被聘为ILLIAC IV的主任。

这台机器刚到的时候,不能让它运转。它遭遇了各种各样的问题,从开裂的PCB,到糟糕的电阻器,再到TI IC的封装对湿度高度敏感。这些问题得到了缓慢的解决,到1973年夏天,第一批程序能够在系统上运行,尽管结果令人高度怀疑。从1975年6月开始,一项为期四个月的协调一致的工作开始了,其中需要更换11万个电阻器,重新布线部件以解决传播延迟问题,改善电源中的滤波,并进一步将时钟速度降至13兆赫。在这个过程结束时,系统终于可以正常工作了。[31][2]。

从那时起,系统从周一早上运行到周五下午,为用户提供了60小时的正常运行时间,但需要44小时的计划停机时间。[2]然而,随着美国国家航空航天局(NASA)的程序员学会如何从这个复杂的系统中获得性能,它被越来越多地使用。起初,性能令人沮丧,大多数程序的MFLOPS约为15%,约为CDC 7600平均运行速度的三倍。[37]随着时间的推移,这一点得到了改善,特别是在Ames程序员编写了他们自己版本的FORTRAN、CFD并学习了如何将I/O并行到有限的内存之后。在可以并行化的问题上,这台机器仍然是世界上最快的,性能比CDC 7600高出两到六倍,直到1981年,它一直被普遍认为是世界上最快的机器。[31][31]。

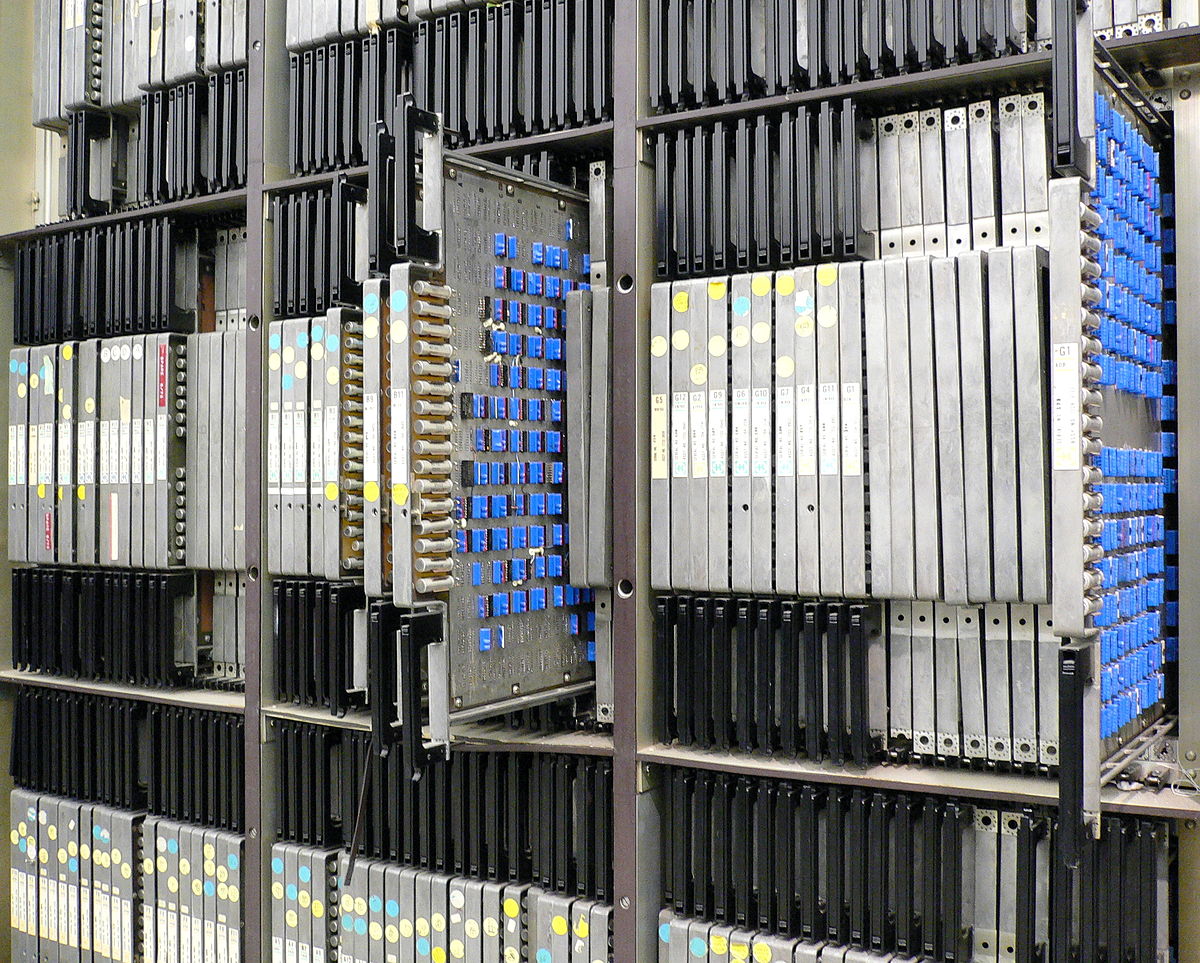

1981年9月7日,在运行了近10年后,ILLIAC IV被关闭。[38]这台机器于1982年正式退役,美国国家航空航天局(NASA)的高级计算部门也随之结束。该机器的一个控制单元和一个处理单元机箱现在山景城的计算机历史博物馆展出,距离其操作地点不到一英里。[39]

ILLIAC非常晚,非常昂贵,从未达到生产1%GFLOP的目标。它被广泛认为是失败的,即使是那些为它工作的人;其中一个人简单地说,任何公正的观察者都必须将ILLIAC IV视为技术意义上的失败。在项目管理方面,它被广泛认为是失败,超出成本估计四倍,需要多年的补救努力才能使其发挥作用。正如斯洛特尼克后来说的那样:

我深感失望,也非常高兴……。既高兴又沮丧。令人高兴的是,总体目标最终取得了很好的结果。令人沮丧的是,它的成本太高,耗时太长,做得不够,而且没有足够的人使用它。[41]。

然而,后来的分析指出,该项目有意无意地对整个计算机市场产生了几个长期的影响。[42]。

间接影响之一是ILLIAC项目之后半导体存储器的快速更新。斯洛特尼克在选择飞兆半导体生产存储IC时受到了很多批评,因为当时生产线是一间空房间,设计只存在于纸上。[43]然而,经过三个月的紧张努力,仙童有了一个正在批量生产的工作设计。正如斯洛特尼克后来评论的那样,仙童做了一件了不起的工作,把我们的栗子从火中拉了出来。仙童的记忆非常出色,直到今天它们的可靠性也令人难以置信地好。ILLIAC被认为对核心存储器和相关系统(如薄膜)造成了致命的打击。[29][29]。

另一个间接影响是由印刷电路板(PCB)或模块的复杂性造成的。在最初25兆赫的设计速度下,地线的阻抗被证明是一个严重的问题,要求PCB尽可能小。随着其复杂性的增加,PCB不得不增加越来越多的层,以避免变得更大。最终,他们到达了15层深,这被证明远远超出了绘图员的能力。设计最终是使用分包商提供的新的自动化设计工具完成的,整个设计需要在Burroughs主机上花费两年的计算机时间。这是计算机辅助设计向前迈出的重要一步,到20世纪70年代中期,这样的工具已经司空见惯。[44][44]。

ILLIAC还导致了对具有广泛影响的并行处理主题的主要研究。在20世纪80年代,随着根据摩尔定律微处理器的价格下降,许多公司创造了MIMD(多指令、多数据)来建造更多的并行机,编译器可以更好地利用并行性。思维机器CM-5就是MIMD概念的一个很好的例子。正是由于对ILLIAC上的并行性有了更好的理解,才导致了I。

..