芯片收缩:英特尔如何缩减8086处理器

革命性的Intel8086微处理器是42年前的这个月推出的,所以我一直在研究它的芯片。1我遇到了两个大小不同的8086芯片,它们揭示了芯片如何收缩的细节。芯片收缩的概念是,随着技术的进步,制造商可以缩小硅芯片,从而降低成本和提高性能。但它不仅仅是简单地缩小整个芯片的尺寸。虽然内部电路可以直接缩小,但两个面向外部的特征可以。例如,键合焊盘需要最小尺寸才能连接导线,配电线必须足够大,以适应当前的电流。结果是,英特尔原封不动地调整了8086的内部尺寸,但重新设计了芯片边缘周围的电路和焊盘。

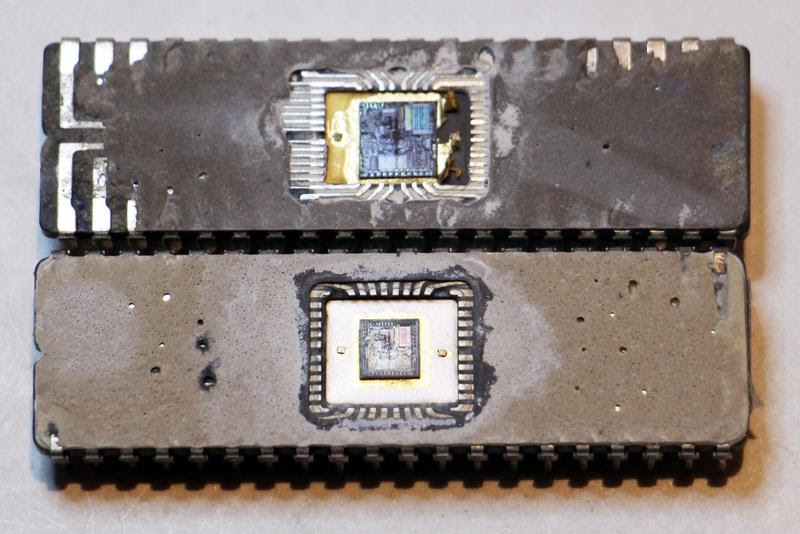

下面的照片显示了1979年的8086芯片,以及1986年的芯片尺寸明显较小的版本。(陶瓷盖已被去掉,以显示内部的硅芯片。)在更新的8086中,内部电路的长度被缩小到原来尺寸的64%左右,因此它占据了原来面积的40%。整个芯片并没有减少那么多;它大约是原来面积的54%。(芯片的封装没有改变,也就是那个时代微处理器通常使用的40针DIP封装。)。

两个8086芯片的比较。底部较新的芯片有一个小得多的芯片。每个芯片右上角的矩形是微码ROM。

8086是有史以来最有影响力的芯片之一,它开启了x86体系结构,至今仍主导着台式机和服务器计算。与现代CMOS处理器不同,8086是由NMOS晶体管构建的,6502、Z-80和其他早期处理器也是如此。4第一个8086芯片是用HMOS-5制造的,这是英特尔的名字,英特尔在1979年引入了改进的HMOS-II,1982年,英特尔转向HMOS-III,这是较新的8086芯片使用的工艺。6每个较新的HMOS版本都缩小了芯片上的功能尺寸并提高了性能。

8086的两个版本在相同的比例下下模。焊线连接到芯片边缘周围的焊盘上。

上图显示的是两个8086的死亡比例相同。这两个芯片的内部布局相同,7尽管它们一开始看起来可能不同。右边的芯片在中间有许多黑线,左边没有出现,但这是一件艺术品。这些线是金属下面的多晶硅层;左边的芯片有相同的布线,但非常微弱。我认为较新的芯片有更薄的金属层,使多晶硅更明显。

下面放大的照片显示了两个芯片上相同的电路。这两张图片中的元件之间有精确的对应关系,表明电路尺寸缩小了,而不是重新设计。(这些照片显示了芯片顶部的金属层;在右边的照片中可以看到一些多晶硅。)。

然而,芯片的边缘有很大的不同。外部的焊盘靠得更近,尤其是在右下角。这有两个原因。第一,焊盘不能收缩很大,因为它们需要足够大的尺寸来连接焊线。第二,边缘周围的功率分布线更宽,以支持必要的电流。(例如,查看右下角微码ROM的右侧。)部分原因是由于芯片边缘的电源轨迹较宽,以支持必要的电流。(例如,查看右下角微码ROM的右侧。)部分原因是,芯片边缘周围的电源迹线较宽(例如,查看右下角微码ROM的右侧),这部分原因是因为芯片边缘需要足够大的尺寸才能连接焊线。(例如,查看右下角微码ROM的右侧。)。外部的走线需要接上松弛的部分。此外,新芯片中较薄的金属层在不加宽的情况下不能承受同样大的电流。

键合焊盘和相关的晶体管,比较旧芯片(左)和新芯片(右)。在版权日期内,6&34;的顶部奇怪地平坦;看起来好像他们把1985&34;改成了1986&34;。

上面的照片显示了一个连接了焊线的焊盘。驱动晶体管在焊盘上方。较新的芯片有几乎相同大小的焊盘,但功率驱动晶体管都缩小并重新设计。请注意,较新的芯片上的金属电源线要粗得多。英特尔的标识从右下角移到了左下角,可能是因为那里有空间。

首先,介绍一下8086和那个时代的其他芯片中使用的NMOS结构的背景。这些芯片由硅衬底组成,在衬底上掺杂(扩散)砷或硼形成晶体管。在顶部,一层多晶硅形成晶体管的栅极,并提供元件之间的布线。最后,顶部的一层金属层将元件连接起来。

半导体工艺(如HMOS-III)对硅、多晶硅和金属层上的特征的最小尺寸和间距有特定的规则。通过仔细观察芯片,我们可以看到这些特征如何与HMOS I和HMOS III的设计规则相对应。下表(来自HMOS III Technology)总结了不同HMOS工艺的特征。每个版本的特征都变得更小,性能也更好。(从HMOS-II到HMOS-III,英特尔的整体性能提升了40%。)。

下面的显微镜照片显示了老款8086芯片中晶体管的复杂排列。深色区域是掺杂硅,而白色矩形是晶体管栅极。(这张照片中大约有21个晶体管。)一个关键的测量是沟道长度,即源极和漏极之间栅极的长度。(这是白色矩形的较窄尺寸。)我测量了这些晶体管的3μm,这与HMOS I的公布值很好地匹配。这表明该芯片是用3μm工艺制造的;相比之下,处理器采用的是3 MOS m工艺。

旧的8086芯片中的晶体管。为了这张照片,金属和多晶硅被移除了。圆是连接到金属层的过孔。

下面的照片显示了相同尺寸的较新的8086中的晶体管;晶体管要小得多。线性尺寸缩小了64%,所以晶体管的面积是原来的40%。因为我处理这个芯片的方式不同,多晶硅仍然留在芯片上,黄线。掺杂的硅看起来略带粉红色,比以前看起来更不明显。我测量的栅长为1.9μm,是之前3μm的64%。请注意,HMOS-III支持小得多的1.5μm沟道长度,但由于一切都收缩了相同的64%,所以沟道长度。但这比完全重新设计芯片要容易得多。

后来的8086芯片中的晶体管。在硅或多晶硅与金属(已被去除)之间有许多通孔。

我还观察了金属层中的线间距(间距)。下面的照片显示了旧芯片中的一些水平和垂直金属线。我测量了金属线的间距为11μm,这与公布的HMOS数字相符。缩小到64%会在新芯片上产生7μm的间距,尽管HMOS III支持6.4μm。和以前一样,恒定的收缩系数没有充分利用新工艺。

旧的8086芯片的金属层。在金属下面可以看到略带红色的多晶硅布线。

最后,我看了一下多晶硅布线的间距。下面的照片显示了较旧的8086型;多晶硅已经被移除,留下了微弱的白色痕迹。这些平行的多晶硅线可能形成了一条总线,将信号从芯片的一个部分传送到另一个部分。我测量了多晶硅线的间距为7μm,与HMOS公布的数字相符。(有趣的是,根据HMOS规则,多晶硅布线的密度可以比金属布线更密集。)较新的芯片的多晶硅间距为4.5μm,而可能的多晶硅间距为4μm。

芯片收缩提供了一种无需完全重新设计就可以提高处理器性能和降低成本的方法。然而,比较两个芯片可以看出,芯片收缩比统一收缩整个芯片要复杂得多。虽然大多数电路都是直接收缩的,但焊盘没有收缩到相同的程度,因此需要四处移动。电源分配也进行了调整,在芯片外部增加了更多的电源布线。

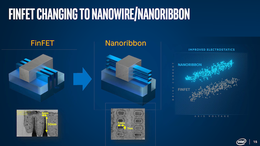

现代微处理器仍然使用芯片收缩。2007年,英特尔转向了滴答模式,在这种模式下,他们将现有芯片(滴答)的缩水与生产新的微体系结构(滴答)交替进行。

我计划在未来的博客文章中更详细地分析8086,所以请在Twitter上关注我@kenshiriff以获取更新。我还有一个RSS订阅源。

MOSFET电路在很大范围内缩小后仍能正常工作,这实际上是相当了不起的,因为大多数东西都不容易缩放。例如,你不能将发动机缩小10倍,然后期望它能工作。大多数物理事物都遵循平方立方定律:面积与比率的平方成正比,而体积与比率的立方成正比。然而,对于MOS电路,大多数事情要么在缩放时保持不变,要么变得更好(如频率和功耗)。有关缩放的更多细节,请参阅Mead和Conway;The Introduction to VLSI Systems CH1 Sector 2有趣的是,1978年的那本书说,由于物理效应,缩放的基本限制是通道长度为1/4微米。这个限制是大错特错的;通过FinFET等技术,晶体管现在正在移动到5 nm。-↩。

对早期处理技术的简要描述。N沟道MOSFET是一种特殊类型的MOSFET晶体管。与最早的微处理器(如Intel4004)中使用的P沟道MOSFET相比,它们的性能要好得多。(现代处理器同时使用N沟道和P沟道晶体管以降低功耗,这就是CMOS。)由N沟道MOSFET构建的栅极需要一个由晶体管实现的上拉电阻。耗尽负载晶体管是20世纪70年代中期引入的一种晶体管,它作为上拉电阻性能更好,不需要额外的电源电压。最后,MOS晶体管最初使用金属作为栅极(MOS中的M)。但在20世纪60年代末,费尔柴尔德开发了用多晶硅代替金属作为栅极的方法。这是因为在六十年代末到七十年代中期,MOS集成电路的生产发生了几次根本性的变化,导致了6502、Z-80、8085、8086等早期处理器的成功。在20世纪80年代,cmos处理器因其更低的功耗和更好的性能而被取代。↩

奇怪的是,我们并不清楚HMOS代表什么。我找不到英特尔在任何地方扩展首字母缩写的地方,这个首字母缩写指的是英特尔先进的N沟道硅栅HMOS工艺,或者说HMOS是一种高性能的N沟道MOS工艺。英特尔后来将CHMOS定义为互补的高速金属氧化物半导体(例如)。摩托罗拉将HMOS定义为高密度MOS(例如),而其他来源将其定义为高速MOS或高密度、短沟道MOS。英特尔在高密度/高速MOS工艺和器件上拥有专利,因此可能HMOS同时代表高密度和高速↩。

有趣的是,在微处理器和其他芯片使用4K静态RAM芯片之前,英特尔使用了4K静态RAM芯片来开发他们的每个HMOS工艺。它们可能是用RAM芯片开发的,因为它具有密集的电路,但相对容易设计,因为它反复重复相同的存储单元。一旦他们弄清楚了所有的设计规则,他们就可以创造出复杂得多的处理器。-↩。

我缩放了两个芯片的完整的高分辨率图像进行比较,除了一些细微的变化外,芯片的主要部分是完全匹配的。我发现了几个通孔轻微移动的地方,这很令人费解,因为我看不出有什么合乎逻辑的原因。电路是不变的,所以它不是一个错误修复。一个问题是微码是否有任何变化。微码看起来一模一样,但我没有逐位比较。--↩