FPGA软核SoC枪战

通常,在FPGA中拥有CPU是非常方便的。虽然有些电脑出售时带有集成CPU,但大多数都不是。一种流行的选择是使用所谓的软核CPU,即在FPGA逻辑中实现的CPU。我决定看看几个流行的和一些不太受欢迎的,看看它们有多容易使用,它们有多快,哪些可能是一个项目的好选择。

我有几个要求任何中央处理器必须满足:1。必须有一个GCC或llvm编译器可用2。没有供应商特定的中央处理器,一个中央处理器应该运行在所有的现场可编程门阵列,如果可能的话,一个简单的准备去的SoC与通用异步收发器,定时器和图形输入输出是不错的,但没有要求。

遗憾的是,S1内核和Swerv EH1不适合我的艺术板。我试着把它们弄得足够小,但我需要艺术A7-100,所以如果有人想赞助我的话;)。

这仍然意味着总共有6个,而且很可能还有其他一些我错过的好选择。

从文档来看,我的直觉是VexRiscv、LEON3和Neo430将是最好用的。我想说的是,微瓦、ZPU和PicoRV32更多的是以业余爱好为导向的。但让我们不要操之过急,我们将更详细地研究每个核心。

使用软核CPU时,我希望快速轻松地启动和运行。如果需要,我还希望能够添加新的外围设备或类似设备。

速度是一个有点难的问题。有时需要超小的CPU来取代几个状态机,有时需要功能更强大的CPU。我决定使用仍然流行的Dhrystone基准测试和FPGA大小来查看性能,这样人们就可以选择他们需要的东西。我列出了以下在软核CPU中寻找的东西:

易于启动和运行我不想花几个晚上的时间来启动和运行一个示例。更换针脚以匹配我的电路板,它应该在运行。

可用的调试器/引导加载器在每次代码更改时生成所有内容并不有趣。理想情况下,CPU中的GDB JTAG会很好,但某种引导加载程序也很好。

容易添加新的外围设备经常在FPGA中使用CPU时,需要添加新的外围设备。我更喜欢像Wishbone这样的已知总线,这样很容易连接新的外围设备。

最大速度正常。我撒谎了,速度越快并不总是越好。最高频率为10 Mhz的CPU可以执行1DMIPS/Mhz的速度比运行在100 MHz、速度为0.5DMIPS/Mhz的CPU慢得多。

混合使用Verilog和VHDL的语言并不总是很有趣,因为并不是所有的模拟器都能处理它。我没有具体的偏好,但目前自由/开源软件工具更喜欢Verilog,不过这一点正在研究中,在不久的将来可能不会有什么问题。

我正在使用我的Digilent Arty板测试每个CPU。我将使用Vivado并创建一个Vivado项目,或者,如果有可用项目或可以生成项目,则使用该项目。

为了测试添加外设有多容易,我制作了一个小型RGB LED外设。它有一个32位寄存器,其中使用24位,8位红色,8位绿色和8位蓝色。它在此基础上产生红、绿和蓝的PWM信号。我用SpinalHDL制作了这个外设,因为它可以很容易地制作Wishbone、AXI、AHB和其他总线外设。

第一个CPU的时间到了。我在SpinalHDL上工作过,也很享受工作,所以他们的CPU Vexriscv似乎是一个很好的起点。有两种可用的SoC,Briey和Murax SoC。Briey SoC是一个更复杂的设计,带有SDRAM,甚至VGA.。我选择了Murax SoC,因为它的设计更简单。

SpinalHDL生成VHDL或Verilog,生成Murax SoC非常容易。我只需要运行一个命令,结果就会生成一个巨大的Verilog文件。我在Vivado中创建了一个新项目,添加了这个文件和一个包含钉住的约束文件。按下生成比特流,喝点咖啡然后砰的一声。SoC。它甚至在第一次就起作用了。

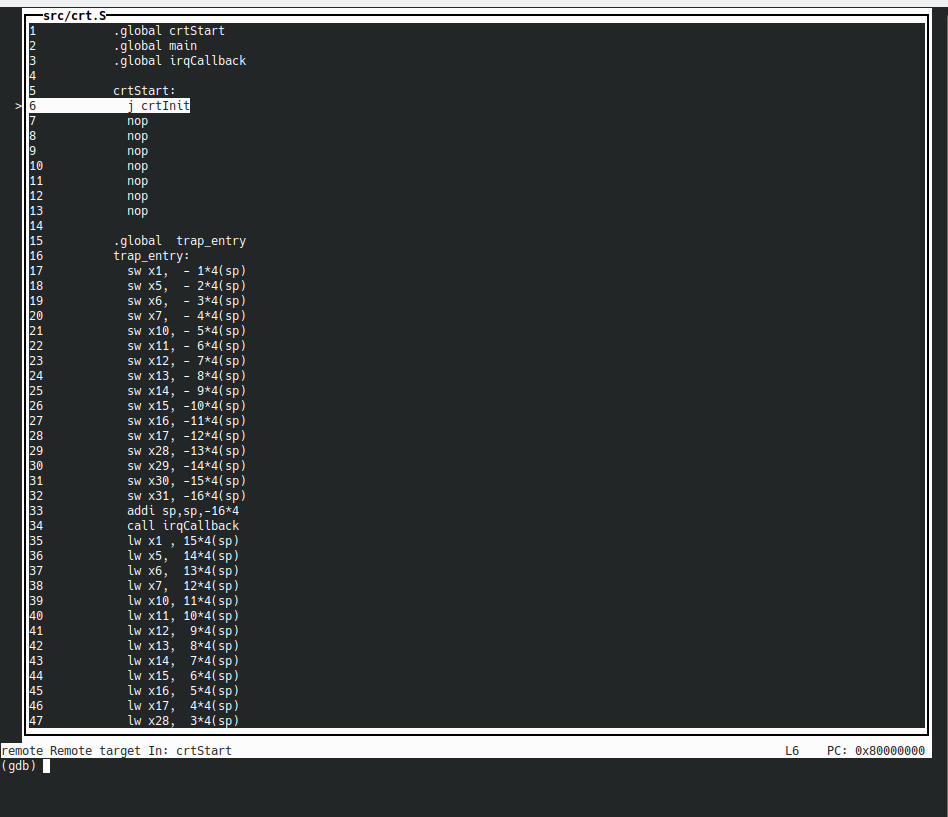

所以让它快速启动和运行是个好点子。现在进行调试:Murax SoC包含一个支持GDB的JTAG调试器。我连接了一个FT232H模块作为调试器,然后出现了问题。需要带有SpinalHDLS补丁的OpenOCD,它以源代码的形式提供,而不是预编译的二进制文件。因此,我需要下载并编译OpenOCD,并在我通常使用的OpenOCD旁边管理另一个OpenOCD。最重要的是,它甚至不能在Ubuntu20.04上编译。幸运的是,一个问题已经打开并包含修复程序。在这之后,这个快乐的屏幕迎接了我。

这里有一些Murax的示例代码,使用SiFive的预编译RISCV工具链编译这些代码没有任何问题。为了添加我自己的外围设备,我根据Murax示例创建了一个新项目,但删除了一些我不使用的部分。我不需要生成5个不同的目标,只需为我生成一个:)添加RGB外围设备并不是太糟糕,只是与在Verilog或VHDL中工作不同。这是与其他CPU相比的缺点之一,使用它可以帮助您学习一些SpinalHDL。稍稍坐立不安之后,我就在RGB LED上眨了眨眼睛。

Vexriscv本身具有很强的可配置性,从Murax中使用的小型CPU到支持Linux的CPU,一应俱全。

如果没有一些基准,就无法测试内核。Murax可以构建为默认或快速内核,但由于它的目标是成为一个小内核,因此性能并不是惊天动地的。Vexriscv支持1.57DMIPS/Mhz,但Murax SoC承诺0.45或0.65DMIPS/Mhz,具体取决于构建配置。我得到了0.52和0.75DMIPS.Mhz。就环境而言,ARM M0可达到1DMIPS/Mhz左右。

就大小而言,在快速配置中,整个SoC使用1206个LUT和第1373个触发器,换句话说,大约占FPGA的5%。CPU本身只使用769LUT和665FF,当我构建它的尺寸时,整个SoC是1074LUT和1338FF,CPU只有648LUT和630FF。就速度而言,整个SoC的默认和快速设置的最高速度是146/127 Mhz。

总而言之,我相当喜欢Vexriscv CPU和Murax SoC。它们可以定制成小型CPU或具有相当高性能的CPU。我确实认为有一些地方仍然可以改进。首先,必须编译OpenOCD可能会很麻烦,提供预编译二进制文件会很好。其次,SoC的外围设备没有很好的文档记录。

我个人喜欢SpinalHDL,但我可以理解不是每个人在尝试CPU时都想学习一门新语言。幸运的是,这里也可以找到预先生成的内核。

我会直接跳到下一个,LEON3。LEON3是用VHDL编写的SPARC V8兼容CPU。LEON3是一款成熟的CPU,已经在ASIC甚至太空中得到了广泛的应用。它捆绑了很多额外的库来制作SoC,所以让我们试一试。

下载中包含许多针对不同开发板的示例项目、一些示例软件和大量文档。例如,附带的外围设备都有很好的文档记录,CPU也是如此。我很高兴看到这一点,因为情况并不总是如此。我也喜欢用来配置SoC的工具。执行make xconfig之后,您会看到一个GUI来调整SoC。

我的艺术板的示例启动并运行得很快。这给了我一个看待调试器的机会。调试器不是通常的JTAG和GDB组合,而是称为GRMON的自定义调试器。GRMON可以使用不同的接口,在我的例子中,我使用串行端口连接到CPU。GRMON工作得非常好,提供了一个非常可用的命令行界面来与SoC交互。GRMON的评估版本确实缺少一些功能,比如GUI,但是它足够好,可以试用CPU。它甚至读取SoC信息并将其显示在命令行中。

编译我自己的代码没有那么快。编译器套件可以在线下载,但是编译一些代码得到的二进制文件不正确。同样不错的是,构建该软件的Makefile似乎不起作用。经过反复试验,我发现这个很棒的存储库包含了正在运行的makefile和dhrystone程序,非常不错。

我已经谈到了定制SoC,它通过一个很好的GUI工具工作。但我也希望能够添加我自己的外围设备。LEON3使用APB3总线,幸运的是我用SpinalHDL制作了PWM外围设备,它也支持该总线。经过快速更改和稍后生成后,我有了APB3版本的外设。然而,让它工作并不像我想的那样顺利。

GRMON工具读出的漂亮信息屏幕肯定来自某个地方,事实上,每个外围设备都有供应商和类型,如果没有供应商和类型,似乎就无法工作。我添加了None Existing Vendor/type,但GRMON的评估版本仅支持某些供应商/类型。我给PWM外设提供了与随附的定时器外设相同的供应商/类型,并且工作正常,尽管信息屏幕没有那么有用。

另一件重要的事,就是性能。我得到了0.84DMIPS/Mhz,比承诺的1.4DMIPS/Mhz要低。我尝试了一下配置,但无法获得更多,可能是编译器设置或诸如此类的错误。遗憾的是,关于1.4DMIPS/Mhz是如何实现的,没有确切的信息,所以很难重现。对于这个CPU,我的ARTY上的最大时钟速度大约是85 Mhz。

LEON3是一个有点大的SoC,时钟频率为5505LUT和2224FF,CPU在4542 LUT和1552FF中所占比例最大。

LEON3不是最小也不是最快的SoC,但它得到了很好的支持。文档非常好,能够获得商业支持可能非常方便。不过,示例代码可能是可以改进的。

我很喜欢LEON3SoC。这可能不是SoC最好的爱好,而且它相当大,但对于专业工作来说,它看起来是一个很好的选择。

另一款RISC-V CPU,在这方面很受欢迎。PicoRV32是一款RISC-V CPU,目标是高时钟速度和小尺寸。因此,性能相对较慢。PicoRV32是一个单一的verilog文件,还包括wishbone和axi版本的CPU。

一个示例SoC EXIST,意指ICE40 FPGA EXIST,称为picosoc。这使用ICE40开发板上的闪存,对端口来说似乎很麻烦。相反,我决定制作自己的SoC,这能有多难:)我在PicoRV32的Wishbone变体周围创建了一个SpinalHDL包装器,并添加了一些外围设备,当然包括我的RGB外围设备。因为我之前在Spinal做了几个小的叉骨外围设备,所以我在大约两个晚上有一个工作的SoC。

我没有调试器或引导加载程序,但这类似于picosoc。编译代码结果比我希望的要更烦人一些。我已经从Vexriscv安装了RISCV工具链。但是,示例makefile使用不同版本的工具链。其中包含一个下载和编译工具链的脚本,但是还有另一个工具链有点烦人。除此之外,多亏了Wishbone接口和SpinalHDL,SoC的制作变得相当顺利。

因为我做了SoC,所以我不能研究SoC的定制。但是,我可以考虑自定义PicoRV32CPU。PicoRV32内核可以配置为非常小的CPU。它甚至可以只与16个寄存器(RISC-V e内核)一起使用,并且所有选项都打开,它支持乘法和压缩RISC-V ISA。支持简单的内存接口以及Wishbone和AXI也有助于定制。

正如我在PicoRV32简介中提到的,它并不是一个非常快的CPU。在GitHub上,未查看前瞻内存接口时提到的速度为0.305DMIPS/MHz。如果使用该接口,则速度为0.516DMIPS/Mhz。在实践中使用我的SoC时,我得到了0.2DMIPS/Mhz。这很可能是因为Wishbone接口是一个瓶颈。我还尝试禁用乘法和压缩指令支持,得到0.188DMIPS/Mhz。

不过,时钟速度更令人印象深刻。我的SoC在禁用倍增和压缩的情况下得到了170兆赫的频率。启用这些功能后,我得到了大约130兆赫的频率。

看看大小,乘法/压缩禁用,我的整个SoC是1134个LUT和889FF。CPU占用1000个LUT和701FF。在启用乘法和压缩ISA的情况下,CPU需要2011个LUT和1213个帧。

PicoRV32是一种流行的爱好CPU,有一些很好的理由。它的CPU大小非常可配置,并且支持多条总线。然而,在软件方面,可以采取一些步骤。没有准备好在各种主板上使用SoC也有点令人沮丧。

在查看另一个流行的RISC-V CPU Vexriscv时,我没有看到使用PicoRV32的太多理由。Vexriscv很小,有两个不同的SoC,并且有一个GDB调试器。

在所有32位CPU之后,是16位CPU的时间了。NEO430是与TI MSP430系列兼容的CPU。MSP430有望成为SoC那样的小型微控制器,让我们来看看。

NEO430更像是一个微控制器,而不是CPU,因为它配备了很多外围设备。例如,完全配置时,它包括I2C、SPI、定时器等。

使用NEO430是一次很好的体验。没有示例项目,但我需要做的就是添加所有的VHDL文件并正确设置管脚。通过顶层的几个泛型启用或禁用外围设备,使定制变得容易。NEO430没有调试器,但默认情况下它有一个相当方便的引导加载器。它甚至有一个很棒的菜单:

编译和运行代码也没有什么大问题。工具链可以从TI下载,因为它是MSP430兼容的CPU。也有很多示例软件项目可以开始。我也很喜欢文档,它有超过90页的漂亮文档,甚至包括一个很好的入门部分。

在赞不绝口之后,我终于在添加PWM外设时遇到了问题。MSP430支持WISHBONE总线,但是在文档中提到了这一点:

我的叉骨外周一点也不喜欢这个。我不得不稍微改变一下,才能让它启动和运行。另一件有点令人沮丧的事情是,外围设备都修好了。我可以禁用或启用UART,但不容易添加第二个UART。

有点慢。在启用乘除的情况下,我得到了0.154DMIPS/Mhz。NEO430并不自称速度快,它自称很小。而且它确实很小。整个SoC只有863个LUT和821个FF。CPU只有420个LUT和126个帧,不错。就时钟速度而言,在我的艺术板上,SoC可以运行在100 MHz。

我很喜欢这个小CPU。有很多值得喜欢的地方。它的启动和运行非常顺利,文档非常棒,而且非常小。NEO430不是块上最快的CPU,但当你不需要CPU的数字处理器时,它是很棒的。然而,有一个小的潜在问题。

NEO430使用MSP430指令集,它不像RISC-V或SPARC那样是免费的开源指令集。另一方面,MSP430已经相当老了,所以专利可能已经用完了。对于业余爱好,这可能没问题,但对于商业用途,与法律顾问进行简短的交谈可能会很方便。

啊,ZPU。我以前用过ZPU CPU,这是我得到第一块FPGA板的原因之一,这是Papilio板中的一块,这样我就可以玩Zpuino了。ZPU是基于32位堆栈的CPU。它被设计成GCC能瞄准的最小的中央处理器。ZPU是堆栈CPU,这意味着它不像大多数CPU那样具有寄存器。ZPU也有非常少量的强制性指令。许多指令集可以使用一小部分强制指令在软件中进行仿真。所有这些都是为了让它变小。

因为我以前用过Zpuino,所以我试了试。可悲的是,让它在Vivado上运行并没有奏效。GIT repo有点杂乱无章,只有一些旧的斯巴达FPGA的示例项目。幸运的是,ZPU是一个开放的架构,有人开发了ZPUFlex。甚至还有几个外围设备和演示项目,非常不错。

ZPUFlex启动并快速运行。没有调试器或引导加载器,但幸运的是,它的合成速度非常快。让hello world运行得很快,没有什么大问题。

编译代码变得合理。GCC可以二进制下载。然而,zpu是支持GCC的最小的cpu,但是它的版本很好。很古老。GCC 3.4.2是最新版本,从外观上看还没有更新的版本。

为了非常小,ZPUFlex不支持Wishbone或其他总线。支持简单的存储器总线,并且连接外围设备相当简单。

ZPUFlex有大量的配置选项。例如启用或禁用诸如乘法器、仿真指令等部件。

是的,我称它为大小,而不是性能,因为老实说,它没有太多的性能:)ZPU很小。真的很小。带有UART的小型SoC是469个LUT和287个FF,仅CPU就使用369个LUT和189个FF。

表演是,嗯。慢的。在小型配置中,它的速度为0.014DMIPS/Mhz。在50兆赫时,它的速度和1兆赫的Vexriscv一样快。如果使用乘法等选项,它的速度为0.06DMIPS/Mhz。这至少与dhrystone示例中的声明相匹配。在时钟速度上,它在215兆赫左右是最快的,所以这是很了不起的。简单的CPU通常意味着较高的时钟速度,而ZPUFlex与此相匹配。

ZPUFlex内核启动并快速运行,性能与我预期的大致相同。很慢,但很小。ZPU架构是一个奇怪而有趣的架构。遗憾的是,工具链的开发几乎是不存在的,但它绝对是一个有趣的CPU架构。对于小型CPU,NEO430很可能是更好的选择。

不久前,IBM决定将他们的POWER架构开源。这意味着每个人都可以制造和使用功能强大的CPU,这永远是个好消息。MicroWat是一款用VHDL编写的功耗ISA CPU,几乎是同时启动的。

Microwatt使用FuseSoC来支持几块FPGA板,包括我得到的Arty板。这使得生成Vivado项目并试用它变得很容易。最近对ECP5 Lattice FPGA的支持也在进行中,所以可能很快就会支持更多的主板。

SoC包括DDR3内存支持和UART。当我尝试它时,没有调试器或引导加载器,但似乎也在努力使其运行。目前没有计时器,所以为了运行一些基准测试,我添加了一个简单的计时器。软件方面,hello world示例编译时没有任何问题。还有对micropython的支持,这有点巧妙。示例不多,但编写示例的外围设备也不多。

我从添加一个简单的计时器开始。MicroWatt使用Wishbone总线,因此添加计时器非常容易。由于合成微瓦CPU需要一段时间,而且缺少调试器/引导加载程序意味着每次代码更改都需要合成,所以我没有添加PWM外围设备。

MicroWat有几个配置选项,但不能像某些其他CPU那样进行自定义。

让我们看看这个强大的CPU能做些什么。一个快速的Dhrystone基准测试给出了大约0.5DMIPS/Mhz。虽然不是最快的CPU,但也不算太差。他们的GitHub上没有任何声称的速度,所以我不能验证我的结果是否正确。

POWER是一个64位的CPU,这使得它不是一个非常小的CPU。在ARTY FPGA中,微瓦需要7337个LUT和3465个FF。它可以以略高于100兆赫的速度运行。

我认为开源POWER CPU的存在真的很酷。Microwatt仍在积极开发中,在尝试它和写博客文章的这一个月左右的时间里,已经添加了相当多的东西。遗憾的是,文档目前不是一个强项,希望这一点在未来会有所改善。

从大小和性能来看,微瓦既不是速度最快的CPU,也不是最小的CPU。如果我需要FPGA中的CPU,它不会是我的首选。然而,在CPU和CPU架构上有更多的选择总是受欢迎的。

遗憾的是,Swerv EH-1内核不适合我的FPGA。我需要大约两倍的FPGA才能工作。我确实想写一点关于Swerv EH-1内核的内容,因为它是一个有趣的野兽。

西部数据是著名的硬盘公司,将EH-1内核作为嵌入式高性能CPU。他们最近还增加了EL-2,一种SMA。

.