基于实物模具逆向工程的I8080精密复制品在Verilog中的实现

2020-08-10 04:20:00

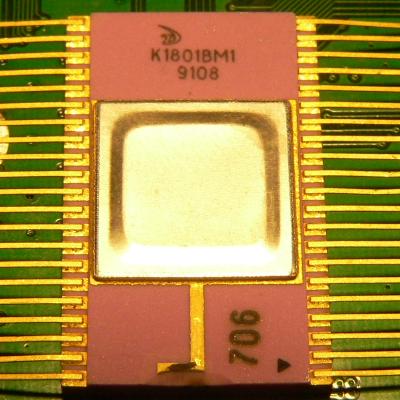

Vm80a是在真正的580BM80A芯片的基础上构建的内核,580BM80A芯片是早期Inteli80A微处理器的苏联复制品,它们在拓扑结构上非常接近。

该项目在Verilog中提供了两个i8080型号-一个与原始处理器管脚兼容,另一个经过重构以在SoC中实现,并具有Wishbone接口。这两种方法都在实板和FPGA上得到了验证。模型足够紧凑和快速,典型的速度和面积是DE0板(Cyclone EP3C16F484C6)上具有Wishbone功能的模型的典型速度和面积:

同步vm80a内核,所有原始计时保持不变,包括用作实际i8080/580BM80a的就地替代的包装器。

Wishbone兼容版本的vm80a内核,使用单时钟,FPGA优化,遵循原始命令执行时序