PCI Express重定时器与Redriver:令人瞠目结舌的差异(2019年)

自近10年前首次引入外围组件接口Express(PCIe)3.0以来,重定时器和重驱动程序已在服务器和存储系统中启用了更长的物理通道。现在PCIe 4.0正在加速发展,PCIe 5.0即将到来,面对高速连接方面的新挑战,这些REACH扩展工具是如何堆叠在一起的?

转接驱动器主要是模拟REACH扩展设备,旨在提升信号的高频部分,以抵消由互连(中央处理单元(CPU)封装、系统主板、连接器等)引起的频率相关衰减。再驱动器的数据路径通常包括连续时间线性均衡器(CTLE)、宽带增益级和线性驱动器。此外,转发器通常具有输入信号损失阈值和输出接收器(Rx)检测能力。图1显示了一个典型的重驱动程序框图。

重定时器是一种混合信号模拟/数字设备,它是协议感知的,能够完全恢复数据、提取嵌入时钟并使用干净时钟重新传输数据的新副本。除了重驱动器中的CTLE级和宽带增益级之外,重定时器还包含时钟和数据恢复(CDR)电路、判决反馈均衡器(DFE)和发射(TX)有限脉冲响应(FIR)驱动器。有限状态机(FSM)和/或微控制器通常管理CTLE、宽带增益、DFE和FIR驱动器的自动适配,并实现PCIe链路训练和状态状态机(LTSSM)。图2显示了一个典型的重定时器框图。

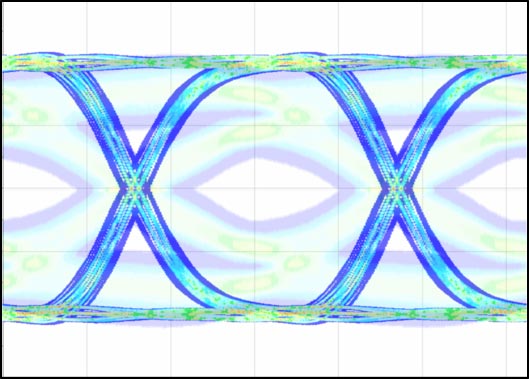

简而言之,重驱动器放大信号,而重定时器重传信号的新副本。图3说明了这一点,并显示了衰减的眼球张开是如何由再驱动器增强并由再定时器完全再生的。

图3:通道衰减的眼睛示例(左)、重驱动程序后的眼睛示例(中)和重定时器后的眼睛示例(右)。

PCIe 4.0规范采取了前所未有的步骤,正式定义了术语“重定时器”、“重驱动程序”和超集术语“中继器”,所有这些都是扩展设备或组件的类型,其目的是延长链路的物理长度。定义如下:

中继器:对延长器的一个不精确的术语[2]。(此术语造成混淆…。请不要使用!)。

重定时器:物理层协议感知、软件透明的扩展设备,形成两个独立的电链路段[2]。

只要通道(根联合体(RC)和端点(EP)之间的电气路径)比PCIe规范允许的长度长,就需要使用到达扩展设备。该规范定义了最大信道长度,其依据是奈奎斯特频率下的插入损耗(信息丰富的规范,但易于验证)和参考接收器充分均衡和恢复数据的能力(假设为最坏情况下的链路伙伴发射机)(规范规范,但验证耗时)。

图4显示了一个双连接器“Riser卡”拓扑示例,该拓扑通常会超过PCIe 4.0 28 dB的损耗预算。重驱动程序或重定时器将实现RC和EP之间可靠、无错误的通信。但是你如何选择哪一个是适合这项工作的工具呢?嗯,更多地了解他们能力上的根本差异是有帮助的。

并非所有重驱动程序和重定时器都相同。两者之间有许多区别,这对于所有PCIe REACH扩展设备都是普遍适用的。例如:

重定时器积极参与PCIe协议;重驱动程序不参与。PCIe基本规范详细说明了在检测、恢复、L0和其他LTSSM状态期间重定时器如何以及在多大程度上参与协议。均衡到L0和L1链路状态需要重定时器的增值功能(握手、超时、位操作等)。雷德里弗斯不知道也不参与该协议。如果第一次链接工作可靠,那就太好了!但是,如果链路经历任何类型的边缘,则由于重驱动程序在链路形成中的角色未定义且其链路伙伴不知道,因此很难精确地确定问题是在重驱动程序之前还是之后。

重定时器重置抖动和插入损耗预算;重定时器不重置。重定时器的CDR完全恢复数据流,并在干净的时钟上重新传输它。从数据的最新副本开始,可以将通道扩展到原始规范的两倍。在没有CDR的情况下,重驱动器最多只能衰减(而不是复位)由符号间干扰(ISI)引起的数据相关抖动(DDJ)。重驱动器不能衰减不相关或随机抖动(RJ)。事实上,由于转接驱动器自身的器件热噪声,转接驱动器总是会以均方根(RMS)的方式增加RJ[1]。

重定时器有DFE;重驱动程序没有。DFE补偿由电路板通孔、连接器和封装插座-电路板接口中的阻抗不连续引起的通道响应中的反射。DFE的优点是它不受串扰的影响。在存在串扰的情况下,DFE也同样均衡,一旦重定时器的CDR对数据进行采样,串扰就会永远消除。雷德里弗斯使用的CTLE同时增强了信号和噪声[1]。串扰不会通过转发器消除,甚至不会减弱;事实上,串扰会被放大。

重定时器自动调整其接收和发送均衡器,以匹配通道特性和链路伙伴的需求;重定时器不能。重定时器将检查其接收的信号,并调整CTLE和DFE以最小化其自身的误码率(BER)。同样,重定时器的发射机将根据PCIe均衡协议调整其去加重和预射均衡,以最小化链路伙伴的误码率。相反,再驱动器以静态均衡器设置操作。在输入/输出缓冲器信息规范(IBIS)算法建模接口(AMI)模拟和实验室测试中进行详尽的搜索之后,通常会费力地选择最佳设置(对于系统中的每个通道可能不同)-这一过程被亲切地称为“调谐”。

重定时器具有内置功能来帮助诊断链路问题(电气和协议问题);重定时器没有。重定时器具有用于评估电气性能(内眼监视器、模式生成器、模式检查器)和协议性能(链路状态历史监视器、超时调整)的工具。Redriver不能提供这样的诊断功能,因为它们既不知道协议,也不知道实际通过的数据。雷德里弗斯不知道链接处于什么状态。

重定时器可以纠正车道间的偏斜;重定时器不能。PCIe对电路板上通道之间的物理偏差有严格要求(PCIe 4.0为1.6 ns),通常由通道布线长度不匹配[3]引起。需要重定时器来补偿并重置通道间的任何偏斜,从而有效地使规格预算翻了一番。Redriver无法补偿通道间的偏斜,更糟糕的是,根据重驱动程序包在所有通道上的对称程度,它们可能会降低偏斜。

重定时器可以放置在两个符合PCIe的通道之间的任何位置;重驱动程序不能。根据定义,重定时器将总PCIe通道覆盖范围扩展为规范的两倍。然而,转向器的伸展范围取决于它在通道中的位置--转向器之前的损耗与转向器之后的损耗之比[1]。转接驱动器的具体位置必须通过IBIS-AMI仿真和实验仔细确定。如果距离根复合体发送器太近,则转向器的CTLE将进入非线性操作,且效益有限。如果转接驱动器的设备噪声距离发射器太远,可能会显著降低数据信号的信噪比(SNR)。

对于重新驾驶来说,也不全是坏消息。与重定时器相比,它们确实具有更低的功耗和更低的输入到输出延迟。但是,如果链路一开始就没有形成,或者误码率太高,这些都无关紧要!

展望即将到来的PCIe 4.0系统,所有迹象都表明,由于以下几个趋势和挑战,对REACH扩展设备(特别是重定时器)的需求将会增加:

与PCIe 3.0相比,CPU的每个插槽具有更多的PCIe通道(在某些情况下为>;100[4])。这会导致更多的PCIe插槽和转接卡、更密集的路由以及更多多连接器拓扑的使用。

PCIe正在从I/O总线转向多用途系统互连。这意味着更多的服务器将被设计成模块化的,从而允许一系列计算、存储和网络资源插入到越来越多的PCIe插槽中。这种开放的、“插入任何东西就可以工作”的服务器体系结构需要一个符合即插即用互操作性的PCIe兼容的REACH扩展解决方案。

模块化服务器、存储托盘和加速器托盘等资源的拆分正在推动端点物理上远离CPU,需要电缆或载波卡将一切连接在一起。这些较长的物理拓扑将越来越需要到达扩展设备。

系统采用多种互连样式-M.2、光纤/铜缆(OCuLink)等-所有这些都具有独特的通道间偏差和串扰挑战,必须由REACH扩展解决方案来解决。

PCIe 5.0紧跟在PCIe 4.0之后,整个行业对更高带宽的被压抑的需求将导致PCIe 4.0昙花一现。系统设计人员正在寻找一种可以轻松快速地从4.0扩展到5.0的REACH扩展解决方案。

最后,系统设计人员将从REACH扩展解决方案的多种选择中获益。服务器或存储系统的确切性能要求、物理约束和成本目标将指导决策过程,行业将从了解重定时器和重驱动程序设备之间的权衡中受益。

萨曼,S.,Froelich,D.,和Johnson,S.(2015)。高速串行总线中继器入门:重驱动和重定时器微体系结构、特性和使用[白皮书]。Https://www.intel.com/content/dam/www/public/us/en/documents/white-papers/serial-bus-white-paper.pdf。

为什么AMD EPYC罗马2P将有128-160条PCIe Gen4车道和奖金。Https://www.servethehome.com/why-amd-epyc-rome-2p-will-have-128-160-pcie-gen4-lanes-and-a-bonus/