惠普NanoProcessor:一款甚至不能加法的高速处理器

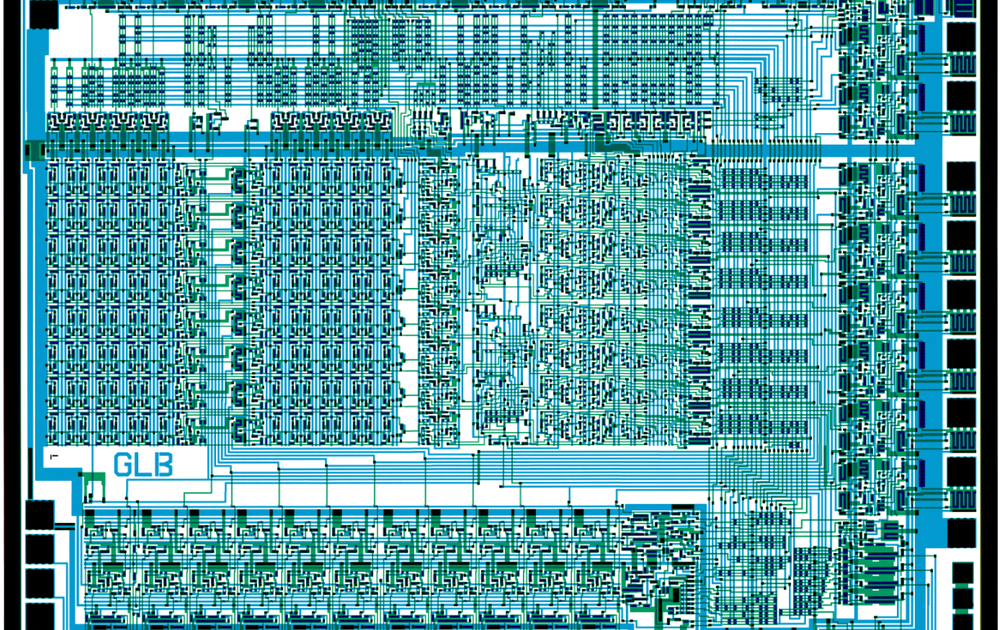

我从掩模中逆向设计了NanoProcessor的电路,并确定了功能块如何映射到裸片上,下面。最大的特征是中央左边的16个寄存器。右边是比较器,然后是累加器,还有它的递增、递减、移位和补码电路。指令译码电路占据了比较器和累加器上方和右侧的大部分空间。芯片的底部由11位程序计数器控制。指令译码电路占用了比较器和累加器上方和右侧的大部分空间。芯片的底部由11位程序计数器控制。指令译码电路占用了比较器和累加器上方和右侧的大部分空间。芯片的底部由11位程序计数器控制。S几乎微不足道的指令时序:一个提取周期,然后是一个执行周期。在大多数微处理器中,控制电路占据了芯片的很大一部分,但是纳米处理器的控制电路只是一小块。

惠普纳米处理器的功能组件,基于我的逆向工程。下面的芯片照片由Pauli Rautakorpi拍摄,CC by 3.0。

该芯片由6个掩模制造而成,每个掩模使用光刻技术构建处理器的一层。下面的照片显示了掩模;每个掩模是47.2×39.8厘米的聚酯薄膜。这些掩模是用于生产4.72×3.98 mm硅芯片的掩模的100倍放大(相比之下,大约比6800的芯片小33%)。每个3英寸的硅片容纳大约200个集成电路,在晶片上一起制造,然后进行测试和切割。这六个掩模是用来制作4.72×3.98 mm硅芯片的(相比之下,大约比6800的芯片小33%)。每个3英寸的硅片容纳大约200个集成电路,在晶片上一起制造,然后进行测试和切割。

为了解释面具的作用,我和#39;我将从用于纳米处理器的晶体管--金属栅MOSFET的结构开始。在底部,掺杂两个硅区域(绿色)使其导电,形成晶体管的源极和漏极。在两个区域之间的金属带形成栅极,由一层薄薄的绝缘氧化物与硅隔开。(这些层--金属、氧化物、半导体--使MOS晶体管得名。)晶体管可以被认为是由栅极控制的开关。金属层还提供了MOS晶体管的主布线。MOS晶体管是由栅极控制的开关。金属层还提供主布线,使其与硅隔开。(这些层--金属、氧化物、半导体--使MOS晶体管得名。)晶体管可以被认为是由栅极控制的开关。金属层还提供主布线。

掩模是集成电路构建过程的关键部分,用于指定元件的位置。下图显示了如何使用掩模在硅片上涂抹区域。首先,将硅片氧化形成顶部的绝缘氧化层,然后涂上光敏光刻胶。紫外光聚合光刻胶并使其硬化(掩模阻挡光线的地方除外)。然后,溶解未曝光的柔软光刻胶。晶片暴露在氢氟酸中,去除了没有光致抗蚀剂保护的氧化层。这会在氧化物上产生与掩模图案匹配的孔洞。晶片随后暴露在高温气体中,该气体扩散到未受保护的硅区,从而改变硅的电导率。这些工艺步骤产生与掩模图案匹配的微小掺杂硅区。如下所示,其他掩模用于不同的工艺步骤,但使用相同的光刻胶和掩模工艺。

我将放大纳米处理器的芯片,并展示它的一个电路是如何由六个掩模构成的。(这个双晶体管电路是一个反相器,反转其输入的二进制值。)第一个掩模使用上述光刻步骤掺杂硅区域,使其导电。掺杂区域(绿色)将成为晶体管源极/漏极或元件之间的布线。

下一步,芯片上覆盖一层绝缘氧化层。第二个掩模(洋红色)用于在氧化物上蚀刻开口,露出下面的硅。这些开口将被用来创建晶体管栅极以及将金属布线连接到硅。

第三个掩模(灰色)暴露在离子注入区域,这改变了硅的掺杂,从而改变了晶体管的特性。这将上部晶体管变成一种特殊的耗尽模式晶体管,将逻辑门输出拉高。

此代码在累加器中获取月份数字(01-12BCD),并(在寄存器0中)返回该月的天数(28、30或31BCD)。即使忽略闰年,对于16字节的代码来说也不是坏事。它是如何工作的?对于过去7个月(7月),它减去1。然后,如果月份是奇数,则它有31天,而偶数月有30天。为了处理2月,代码将清除该月的第1位。如果月份现在是0(即2月),则有28天。

这段代码表明,尽管没有加法的处理器听起来毫无用处,但NanoProcessor的位操作和递增/递减允许进行比您预期的更多的计算。16它还表明,NanoProcessor代码是紧凑和高效的,许多事情可以在单个字节内完成(如位测试和跳过),这在其他处理器上会占用多个字节。12纳米处理器的大寄存器堆也避免了在其他处理器中经常需要的繁琐的数据来回混洗。尽管有些人称纳米处理器更像是状态机控制器而不是微处理器,但这低估了纳米处理器的能力和作用。

虽然纳米处理器不包含算术运算单元或访问RAM的指令,但这些指令可以作为I/O设备添加。时钟模块有256字节的RAM来保存它的多个计数器和计时器值,通过四个I/O端口访问。其他产品增加了ALU芯片来支持算术运算。18岁。

纳米处理器是一种不同寻常的处理器。我的第一印象是,它甚至不是真正的处理器,缺乏基本的算术功能。芯片是用过时的金属栅极技术制造的,落后于其他微处理器几年。最奇怪的是,每个芯片都需要不同的电压,在封装上手写,这表明很难制造一致性。然而,纳米处理器在其微控制器角色上提供了高性能,比当时的其他处理器快得多。惠普在。

虽然纳米处理器一直默默无闻,维基百科上甚至没有提到它,但它的设计者最近披露的面具照亮了处理器历史上这个不同寻常的角落。感谢安托万·贝尔科维奇(Antoine Bercovici)扫描并重新制作面具,感谢拉里·鲍尔(Larry Bower)的捐赠,以及CPU小屋的约翰·卡尔弗(John Culver)分享捐赠。感谢马克·韦迪尔(Marc Verdiell)丢弃时钟板ROM。

我计划写一篇关于NanoProcessor内部电路的文章,所以请在Twitter上关注我,地址是@kenshiriff,以获取有关第二部分的更新。我还有一个RSS提要。

有关惠普纳米处理器及其历史的更多信息请参见CPU Shack';最近的文章《被遗忘的人:惠普纳米处理器》,以及惠普9825.com和惠普9845项目。/↩。

我不太喜欢称纳米处理器为微控制器,因为它使用的是外部程序只读存储器,而微控制器通常将包括只读存储器在内的所有功能都放在一块芯片上。(它在这方面类似于Intel4004。)然而,纳米处理器在大多数方面都类似于微控制器:它是为嵌入式控制应用程序设计的,采用哈佛架构,指令集针对I/O进行了优化,以最小的存储从只读存储器中运行程序。-↩

关于不会加法的计算机的话题,办公桌大小的IBM1620计算机(1959年)没有加法电路,而是使用表格查找来进行加法。它的代号是学员;人们开玩笑说,这代表着不能加法,甚至都不尝试。和↩。

我已经确定纳米处理器用于下列惠普产品(可能还有其他产品):HP 9845B、HP 3585A频谱分析仪、HP 3325A合成器/函数发生器、HP 9885软盘驱动器、HP 3070B数据采集终端、HP 9825计算器的HP 98034 HP IB接口、HP 9825台式计算机的HP 98035实时时钟、HP 7970E磁带机接口、HP 4262A LCR计、HP 3852频谱分析仪和HP 3。

纳米处理器在许多方面类似于RISC(精简指令集计算机)处理器,尽管它比RISC概念早了几年。特别地,纳米处理器的设计具有简单的操作码结构,所有指令在一个周期内执行(在提取周期之后),寄存器集大且正交,并且寻址简单。与更复杂的处理器相比,这些RISC特性产生了更高的时钟速度。“↩。

有趣的是,纳米处理器在开发过程中的竞争对手是摩托罗拉6800,而不是英特尔处理器。纳米处理器的主要特点是性能:它的运行频率为4 MHz,而6800的运行速度为1 MHz。(两款处理器执行一条基本指令都需要2个周期,而6800执行更复杂的指令需要7个周期。)。

纳米处理器的设计者写了一份时序比较报告,估计纳米处理器的计算速度是6800的6倍,处理中断的速度要快16倍以上。该方案假设了5兆赫的纳米处理器,而实际的芯片略低,运行速度为4兆赫。预计纳米处理器的成本为每个芯片15美元,而摩托罗拉6800的成本为360美元。-↩。

纳米计算机的布局密度给我留下了深刻的印象,因为它有局限性:只有一层金属布线,没有多晶硅。我看过其他金属栅极芯片,它们的布局效率非常低,布线比晶体管多得多。但是,纳米处理器的电路安排得很有效,浪费的空间非常少。-↩。

纳米处理器的制造技术在一个方面领先于英特尔8080和摩托罗拉6800:它使用耗尽模式上拉晶体管,比8080和6800中的增强模式晶体管更先进。耗尽模式晶体管产生更快、更低功率的逻辑门,但需要额外的制造步骤。对于纳米处理器,这一步骤使用掩模#3(灰色掩模)。在诸如MOS Technology 6502和Zilog Z-80等处理器中,不幸的是,由于其金属栅极晶体管,纳米处理器仍然需要三个电压。--↩。

早期的DRAM存储芯片和微处理器芯片通常需要三个电源:+5V(Vcc),+12V(Vdd)和-5V(Vbb)。在20世纪70年代末,芯片技术的进步允许使用单一电源。Intel8080微处理器(1974)使用增强型晶体管,需要3个电压,但改进的8085(1976)使用耗尽型晶体管,由+5V电源供电。从70年代末开始,许多微处理器使用。我写了关于

.