ARM更新其Neoverse路线图:新的BFloat16,SVE支持

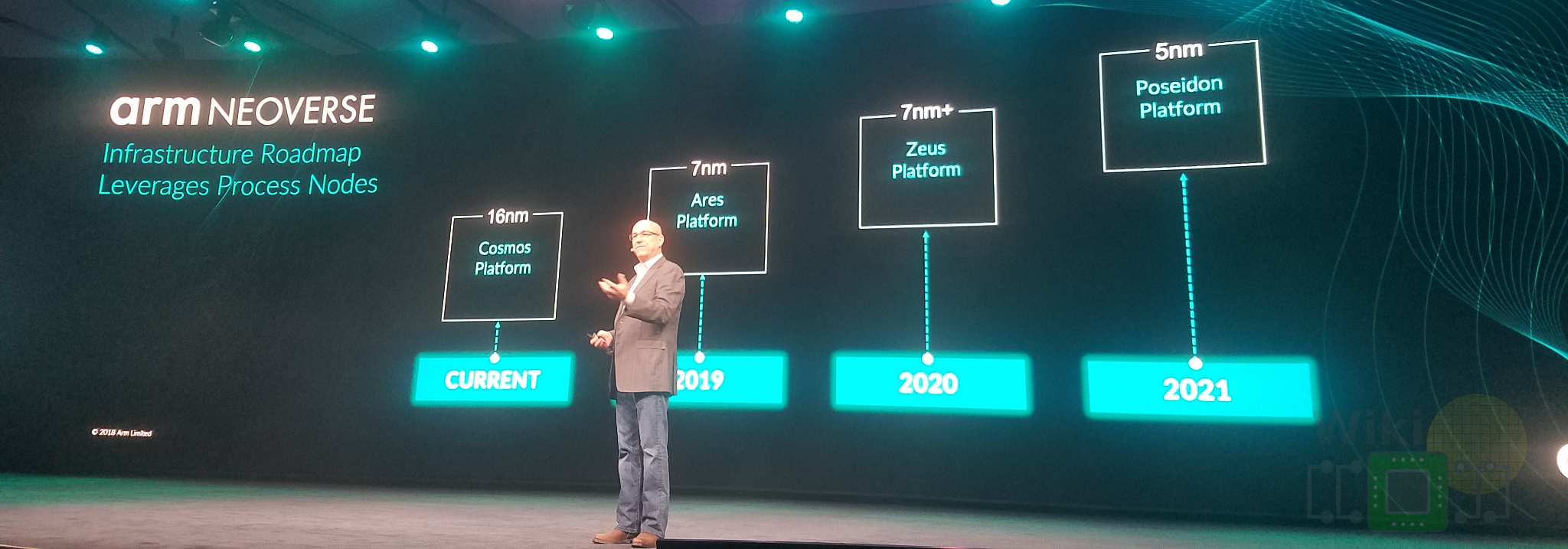

两年前,ARM推出了ARM Neoverse,这是他们针对基础设施的官方举措。在宣布这一消息时,ARM并没有为数据中心提供有吸引力的产品。宇宙平台,简单地说就是针对基础设施进行了调整的Cortex-A72,提供了较低的功率,但没有太多其他的东西。对于数据中心来说,这是一个令人叹为观止的问题,因为性能是关键。ARM确实宣布了一份5年路线图,承诺通过其后续平台Ares、Zeus和Poseidon提供30%的性能或更高的世代更新换代。

去年,ARM推出了代号为Ares的Neoverse N1,这是他们的第一个设计,从Cortex到各种基础设施。N1在单线程性能方面比Cosmos平台提升了60%左右。除了N1,ARM还推出了E1平台,这是一个更轻的核心,旨在通过多线程实现吞吐量。Neoverse N系列本质上是ARM的主流基础架构系列,在数据中心服务器、处理器等产品的TDP范围内具有相当均衡的PPA。Neoverse E系列围绕吞吐量而设计。在这里,动力和面积扮演着前排座椅的角色,驱动着设计,体贴周到。今天,ARM宣布推出一款新的Neoverse系列,名为V系列,性能比任何东西都更能驱动决策。今年早些时候,我们已经看到ARM在他们的Cortex-X系列上采取了类似的举措。这些内核进一步推动了单线程性能,放松了限制主要Neoverse系列的传统PPA限制-即使是以某些面积和功耗为代价。鉴于Cortex-A76和Neoverse N1之间的相似之处,我们可能会预计Cortex-X1和新的Neoverse V1之间会有大量重叠。这一推动显然是为了让ARM客户能够集成一些更强大的内核,并在单线程性能上更好地与即将推出的最好的x86内核竞争。

今天,ARM还发布了V系列的第一个平台Neoverse V1,代号为Zeus。根据他们最初的性能测量,ARM声称与Neoverse N1相比,单线程性能提升了50%以上。由于Neoverse N1在很大程度上是基于Cortex-A76的;如果我们假设Neoverse V1将基于Cortex-X1,那么仅IPC增加50%听起来就非常合理。

虽然这纯粹是一个路线图公告,而不是架构披露,但ARM确实选择分享V1将成为第一个支持可伸缩矢量扩展(Scalable Vector Extension,SVE)的ARM核心。除了主要为HPC市场设计的富士通A64FX之外,我们还没有看到任何其他关于这一延期的承诺,这是五年前首次宣布的。SVE的一个独特之处在于它具有矢量长度不可知的能力(尽管是128位的倍数),允许实现决定最适合其市场的矢量长度。对于Neoverse V1,ARM选择实现两个256位矢量单元。256是一个有趣的选择,原因有几个。首先,这使以前所有ARM设计的SIMD吞吐量翻了一番。Cortex-A78和它的Neoverse N1表亲都有两个霓虹灯管道,每个都是128位的。其次,V1 SIMD单元的宽度是A64FX的一半(以及所有最新实现AVX-512扩展的英特尔大内核),首次允许在实际硬件中对SVE矢量分区进行比较和压力测试。V1还将引入对bfloat16的支持。

在V1发布的同时,ARM还宣布了Neoverse N1的直接继任者,N2平台,代号为Perseus(新代号)。根据他们最初的性能测试,ARM预计在相同的功率和面积效率下,单线程性能将比Neoverse N1提高40%以上。由于最初的Neoverse N1是基于Cortex-A76的,我们可以预计N2将基于最近推出的A78或可能的下一代Cortex(Matterhorn)。鉴于这是一个高级别的路线图公告,而不是架构披露,今天只披露了几个细节。对于N2,ARM预计其横向扩展能力会有显著提高,允许在固定功率预算下以比N1更好的性能获得更多内核。就功能而言,Neoverse N2还将引入SVE支持,但将保留与前几代产品(128B)相同的SIMD单元大小,这意味着我们现在将有三种不同的手臂设计,具有三种不同的SVE SIMD大小。N2还将引入对BFloat16的支持。

像往常一样,很难说我们可以从一张营销幻灯片中推断出多少,但我们想要突出几个有趣的点。例如,下面的幻灯片列出了数据中心的TDP范围从80 W到350 W。这些数字远远超过ARM之前谈论的任何数字(例如,对于Neover N1,甚至对于数据中心,都出现了ARM之前谈论的TDP Range