3 nm以外的晶体管选项(2018)

尽管在成本飙升的情况下芯片规模放缓,但该行业仍在继续寻找5到10年后的新晶体管类型-特别是2 nm和1 nm节点。

具体地说,该行业正在精准并缩小3纳米之后下一个主要节点的晶体管选择范围。根据国际半导体技术路线图(ITRS)2.0版,这两个节点被称为2.5 nm和1.5 nm,计划分别在2027年和2030年出现。另一个组织,Imec,对时间表更为激进,称2.5 nm左右的波长将在2024年到来。

很难预测3纳米以外会发生什么。事实上,3纳米及以上可能永远不会发生,因为在竞技场上有大量的未知和挑战。也许到那时,芯片缩放最终会失去动力。

今天的技术及其未来的迭代甚至有可能提供超过5 nm的足够性能。今天的前沿晶体管类型-FinFET-可能会延伸到5 nm或3 nm,这取决于节点的定义。然后,在4 nm/3 nm,一些人正在转向下一代晶体管技术,称为栅极全能FET,在这种技术中,FinFET放在一边,栅极包裹在它周围。

但该行业也有可能需要新的、更快的设备,而不仅仅是GATE-All-All。许多人认为,在高性能计算、人工智能和机器学习的复兴中,有必要尽可能地推动这项技术。自动驾驶、5G、移动和服务器未来也将需要更大的马力。因此,在研发方面,业界正在研究2.5 nm和1.5 nm的几种技术。在这些节点上,该行业可能会走以下道路:

扩展栅极全能FET或开发该技术的更复杂版本,如互补FET(CFETS)和垂直纳米线FET。

利用现有的FinFET并用新材料调整它们,创造出所谓的负电容场效应管(NC-FET)。

还有其他选择,但现在预测赢家还为时过早。他说:“FinFETs是一项成功的创新。他们至少还有一到两代人。除此之外,我们还有实质性的变化--锗或III-V通道。我们可能有四通八达的登机口。目前还不清楚这些想法中的哪一个最终会取代FinFET,“英特尔高级研究员兼流程架构和集成总监马克·波尔(Mark Bohr)说。

波尔说:“无论我们谈论的是负电容FET、全栅极通道还是III-V通道,你都必须意识到现代逻辑产品有一套非常苛刻的要求。”“获得高机动性是很棒的,但你也必须有低渗漏。您必须具有较低的亚阈值电压和较低的电源电压。所以现在,我不确定有没有哪种技术在今天的CMOS所能做的事情上真的被证明是全面的赢家。在我们选出真正的赢家之前,我们还有其他挑战要迎接。“。

为什么要扩大规模?多年来,增长引擎一直围绕着摩尔定律,即晶体管密度每18个月翻一番的公理。根据摩尔定律,芯片制造商每18个月推出一种新工艺,作为降低每晶体管成本的一种手段。

摩尔定律是可行的,但它正在演变。在每个节点上,流程成本和复杂性都在飞涨,因此现在一个完全扩展的节点的周期已经从18个月延长到2.5年或更长时间。此外,能够负担得起迁移到高级节点的代工客户越来越少。

而且并不是所有的都在向前沿节点转移。对28纳米及以上的需求依然强劲。令人惊讶的是,200毫米晶圆厂的需求依然强劲。“我们继续看到2018年8英寸的需求强劲。它来自不同的应用程序。我们看到移动领域对射频开关、MCU、嵌入式区域以及显示区域的需求特别旺盛。联电联席总裁Jason Wang在最近的一次电话会议上表示:“今天最具挑战性的事情实际上是管理客户,因为现在的需求是压倒性的。”

尽管如此,仍有一些应用程序需要最新的过程,如机器学习、服务器和智能手机。

在另一个例子中,D2S销售基于图形处理器的专用高端系统。该系统用于各种半导体制造应用。D2S首席执行官藤村明(Aki Fujimura)表示:“因此,我们一直处于利用可用计算能力的边缘。”他说:“我可以非常有信心地说,我们不会没有办法使用更多的计算能力来改善半导体制造。我敢肯定,高性能计算的所有其他应用程序领域都处于类似的情况。特别是随着深度学习的兴起,我预测对更高性能计算的渴求将继续上升,远远超过7纳米。“。

然后是需要成熟和先进工艺的应用,比如汽车,当然还有自动驾驶汽车。“有两个不同的生态系统。你有人工智能计算,然后是车辆中的传感器和控制器,“TEL的高级技术人员本·拉萨克(Ben Rathsack)说。“对一些较老的节点技术的需求实际上正在增加。然后,你就有了NVIDIA的处理器。他们可能在做人工智能处理。当然,他们正在推动高端市场。“。

与此同时,制造工具已经为今天的设备做好了准备。但对于2.5 nm和1.5 nm,存在一定的差距。要启用这些节点,该行业将需要以下新技术:

新的光刻技术。7 nm/5 nm需要极紫外(EUV)光刻。然而,在3 nm以外,可能需要一种称为高数值孔径(NA)EUV的下一代EUV技术。

有选择的过程。芯片制造商还需要更广泛的选择性沉积和蚀刻技术,使供应商能够在精确的位置沉积和移除材料。

新的互连方案。芯片中的布线方案太拥挤,需要在竞技场上使用新材料。

然后,在每个节点上,缺陷变得越来越小,越来越难发现。横向缩放,即更密集的晶体管布局,推动了检测较小缺陷的需求,并增加了对设计感知检查和审查的需求。垂直缩放推动了检测和验证隐藏缺陷的需求,“KLA-Tencor营销和应用副总裁Mark Shirey说。

“我们的问题变得越来越困难,也越来越复杂。但这个行业的一个共性是,当你遇到复杂和困难时,这是一个机会,“LAM Research高级副总裁兼技术研究员大卫·亨克(David Hemker)在最近的一次活动中说。

在活动上谈到摩尔定律和其他话题的一般主题时,亨克补充道:“我们对能够在几乎任何设备上从技术上继续使用摩尔定律感到非常乐观。我们看到有很多选择,因为我们想要达到3纳米,甚至更低。“。

发展FinFET今天,芯片制造商正在加速生产10 nm/7 nm的FinFET。在FinFET中,电流的控制是通过在鳍片的三个侧面各实现一个栅极来实现的。

根据ITRS路线图,在7 nm之后,下一个技术节点是5 nm、3 nm、2.5 nm和1.5 nm。然而,这些节点的时序是一个移动的目标,节点名称是任意的,不能反映晶体管的规格。

那么FinFET会持续多久呢?“我们相信FinFET可以持续到大约5纳米的节点。当然,这取决于你攀登大门间距的力度有多大。Imec负责半导体技术和系统的执行副总裁An Steegen说:“如果你把栅距放宽一点,FinFET的寿命会更长。“我们看到纳米片,也就是细长的纳米线,在那之后是一个很好的候选者。”

对一些人来说,FinFET的继任者是称为横向栅极全能FET的下一代技术。计划在2020年左右推出4 nm和/或3 nm,Gate-All-Around是FinFET的一个进化步骤。

栅通绕场效应晶体管的两种主要类型是纳米线场效应管和纳米片型场效应管。在纳米线FET中,沟道使用微细导线。纳米片状FET使用片状材料作为沟道。

全向浇口提供了对浇口的更多控制,从而提高了性能并减少了泄漏。“正是这种改进的浇口控制使你能够继续调整浇口长度,”应用材料公司技术项目董事总经理迈克·丘兹克(Mike Chudzik)说。

使用今天的制造工具和设计技术开发全能闸门装置是可能的。例如,芯片制造商仍然可以利用一种名为设计技术联合优化的成熟技术。

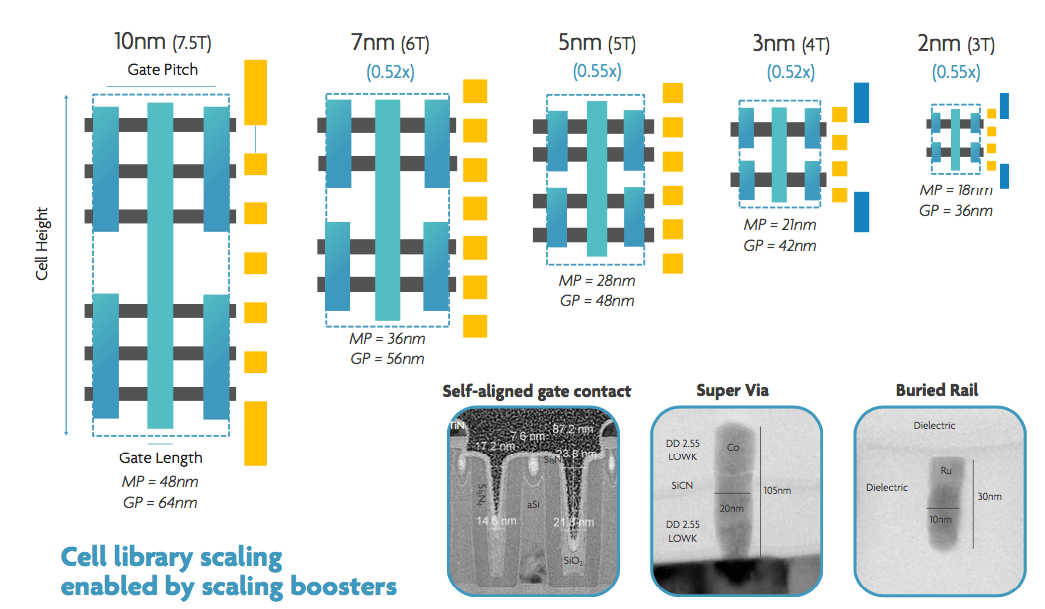

这里的想法是减少每个节点的标准单元格布局中的轨道高度和单元格大小。标准单元是设计中预定义的逻辑元件。单元格以网格形式布局。轨道定义标准单元格布局的高度。例如,根据Imec的说法,7 nm可能具有6道高度单元,使得器件的栅距为56 nm,金属间距为36 nm。

然后,根据Imec的说法,4 nm/3 nm涉及具有5.5-4.5轨道高度的布局,使得器件的栅距从36 nm到42 nm,金属间距从21 nm到24 nm。

根据路线图,横向纳米线/纳米片FET可能从4 nm/3 nm延伸到2 nm左右,这意味着这项技术可能只持续一个或两个节点。

在2 NM处,该行业面临一些障碍。从理论上讲,2纳米的设备将由3轨高度布局组成,但这种类型的方案很难想象,至少目前是这样。Imec的项目主管Diederk Verkest说:“你真的需要至少3个音轨才能制作一个正常的电池。”“有了这种类型的架构,它就变得极具挑战性。”

总而言之,该行业可能需要一个新的解决方案。但芯片制造商不想从头开始。相反,他们更愿意利用现有的工作和制造技术,并对其进行发展。

IMEC提出了两种选择-CFETS和垂直纳米线。CFET的目标波长为2.5 nm及以上,它是一种更复杂的栅极全能器件。传统的全栅场效应晶体管将几根p型导线堆叠在一起。在一个单独的器件中,晶体管将n型导线彼此堆叠在一起。

在CFETS中,想法是将nFET和pFET导线堆叠在一起。CFET可以在pFET线上堆叠一个nFET,或者在两个pFET线上堆叠两个nFET。

由于CFET将n型和p型器件堆叠在一起,因此晶体管提供了一些好处。“主要受益的是面积。面积扩展给您带来了一些功率和性能方面的好处。“Verkest说。“在静电控制方面,CFET将与普通纳米线相同。它们都是通向大门的建筑。“。

其他好处则不太清楚。CFETS将提供面积扩展的提升,但它们的晶体管规格与传统的栅极全能器件大致相同。

CFET更难在工厂制造,可能需要更高的结构。反过来,这可能意味着更高的电容。

另一种解决方案是垂直纳米线FET(VFET)。横向栅极全能FET水平堆叠导线。相比之下,VFET垂直堆叠导线。源极、栅极和漏极彼此堆叠在一起。这意味着面积有所增加。

VFET有一些缺点。VFET是一种扩展SRAM的有效器件。但它不是缩放逻辑单元的设备。

VFET也很难在工厂制造,但这项技术已经在实验室中得到了演示。在IEDM上,Imec、LAM Research和KU Leuven发表了一篇关于垂直纳米片和III-V材料的VFET的论文。在该流程中,使用电子束光刻在结构上形成图案。根据这篇论文,表面被蚀刻,形成直径从25 nm到75 nm的垂直纳米线,形成从1到100纳米线的阵列。

什么是NC-FET?还有其他选择。2008年,普渡大学的研究人员提出了所谓的负电容场效应晶体管(NC-FET)的想法。

NC-FET的目标是3 nm及更远,它并不是一个新器件。取而代之的是,NC-FET采用现有的晶体管,该晶体管具有基于氧化碲的高k/金属栅堆叠。然后,用铁电特性修改栅堆叠,产生远低于60 mV/十年极限的陡峭的亚阈值斜率器件。

平面器件,FinFETs,甚至全栅极器件,只要含有氧化碲,就可以用铁电特性进行修饰。“从本质上说,铁电就像一个电压放大器。你给它加一个电压。因为它相互作用的方式放大了电压。这就是为什么你会得到一个增强的低于门槛的斜率,“应用公司的丘兹克说。

NC-FET与隧道FET(TFET)属于同一类别,TFET是一种未来的陡峭亚阈值晶体管候选。然而,与NC-FET不同的是,TFET需要一种全新的结构。

NC-FET与一种称为铁电FET(FeFET)的技术相关。NC-FET和FeFET都利用了氧化碲的铁电特性。

FeFET和NC-FET是不同的。“最重要的区别是NC-FET是用于逻辑的,而FeFET是用于存储的。原则上,NC-FET是不具有非易失性存储器的逻辑器件。另一种是FeFET,是一种非易失性存储器件,“铁电存储器公司首席执行官斯特凡·穆勒(Stefan Müller)说。(FMC),一家正在开发FeFET的初创公司。

在这两种情况下,铁电材料被夹在另外两种材料之间,并使用沉积将其沉积到基于Hfn的栅堆栈中。“在FeFET中,我们希望将铁电和硅块材之间的缓冲保持在尽可能薄的状态。这与数据保留有关。缓冲层越薄,数据保持性就越好。“Müller说。“NC-FET是不同的。原则上,NC-FET晶体管没有数据保持。这意味着对铁电和硅块之间的缓冲层的要求是不同的。“。

在一个例子中,GlobalFoundries最近发表了一篇关于14 nm FinFET的实验论文,它在栅堆叠中加入了掺杂的Hafnia铁电层。GlobalFoundries称其为14 nm铁电FinFET。它可以分为负电容FinFET和NC-FET。

在14 nm FinFET中,GlobalFoundries测试了厚度为3 nm、5 nm和8 nm的铁电层。他们还测试了1.5 nm的非掺杂层。GlobalFoundries的高级技术人员佐兰·克里沃卡皮克(Zoran Krivokapic)在论文中表示:“我们发现,8纳米厚的薄膜仍然可以生产出功能器件。”他说:“铁电器件显示出低至54 mV/dec的改进的亚阈值斜率。我们首次证明,带有铁电器件的环形振荡器可以工作在与常规介质相似的频率上,而改进的亚阈值斜率则降低了它们的有功功率。“。

不过,NC-FET面临一些挑战。“这里面有很多承诺和兴趣,但也有很多悬而未决的问题。有了闸门,你能放进铁电材料的体积就只有这么多了。铁电体很厚,50到80埃。这将缩小现代FinFET的差距,“应用公司的Chudzik说。“这个行业已经是7纳米了,所以他们需要对这种材料进行缩放,同时仍然要证明它是铁电的。可靠性是一个挑战。然后,由于一些寄生因素,可能会有一些独特的器件设计限制。“。

其他解决方案IC制造商也在寻找芯片缩放的替代方案。一种想法是将多个设备放在一个高级封装中,这样可以以较低的成本提供与扩展设备相同的功能。

有人称之为混合扩展或异构集成。Imec的Steegen说:“我不认为人们会说,‘现在我们将停止使用设备扩展,我们将转向混合扩展。’”“想一想今天的包装和你在包装中堆叠不同芯片的方式。您还可以将其视为混合扩展的一种形式。可以说是从今天开始的。但我们可以继续在这条路上继续建设。“。

下一个是什么?在1.5纳米以外,路线图是多云的。在Imec的路线图上,有几项未来技术,如TFET和自旋波器件。3D纳米芯片(3D NAND的逻辑版本)也是一种可能性。

显然,5 nm以外的问题比答案更多。也许通向大门是答案,或者研究人员会偶然发现一项新技术。当然,到那时,今天的技术可能会持续更长时间,从而推动对这些新奇晶体管的需求。

非常好的文章!我将与我的微电子工程专业的学生分享。我们正在研究其中一些新颖的想法。

有趣的是,似乎没有人关注这些奇异晶体管在切换时产生的数字噪音的未来。从DO到开关的总电流为几百安培。

当我们越过1 GHz的障碍时,我就是这么说的。但是后来我忘了天线太短了,不能接收噪音。

如果能看到一些显示单个原子的晶体管图纸,那将会很有趣。毕竟,原始的硅晶格间距是5.43埃。所以3纳米不会给你太多的原子来处理。

3 nm只是一个营销名称。它可能不对应于设备的任何物理尺寸。

谢谢你,马克。我喜欢读你分享的每一条笔记。我仍然认为,台积电和其他公司的亚7 nm BKM需要审查,以支持从设计到测试周期的新制造制度,以促进这项技术的进步。看来,工业界采用方法的速度还不够快。

谁会在乎FinFET的密度会有多高呢?他们的时钟速度仍然很差。1V线路电压是它们的物理极限。

为什么不考虑选择旧的平面场效应晶体管?好的,不是很老,就让它和哈夫尼亚的FDSOI一起吧。

让我们将其与GAA进行比较:对于给定的斜率,(-)通道稍长;当需要高驱动强度时,DIBL(-)略宽;当不需要高驱动强度时,(+)变窄,例如,为了驱动较少的紧邻浇口,DIBL(-)略宽。(+)输入电容更少-需要的驱动器更少->;允许更薄的互连->;更少的互连电容->;需要更少的驱动器->;更低的功率…。(+)更简单的制造->;…