模拟问题的增加

模拟和混合信号设计一直很困难,但最近的一项调查表明,由于ASIC内的模拟电路超出了容忍度,该行业在过去一年中出现了显著的故障增加。

故障数量激增的原因是什么?这只是数据上的小故障,还是这些问题是真的?答案很复杂,而且在很大程度上依赖于模拟调谐。

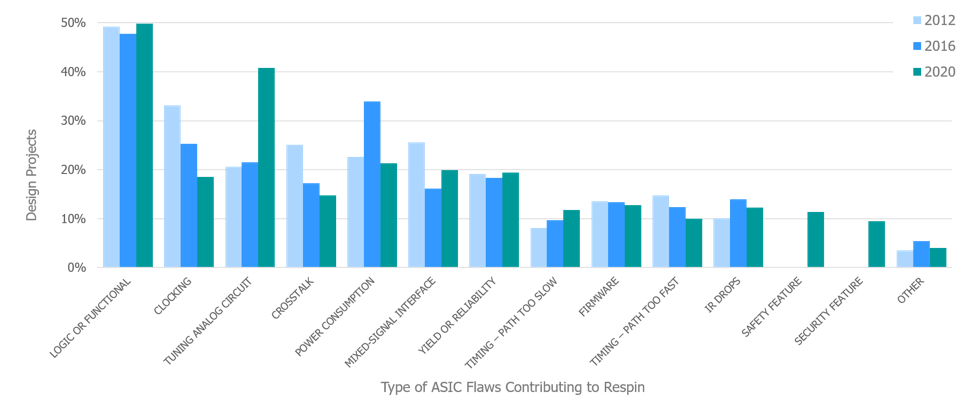

图1:导致ASIC重新旋转的缺陷。资料来源:西门子旗下的Wilson Research and Mentor。

西门子公司Mentor的AMS验证高级产品经理萨蒂什·巴拉苏布拉米安(Sathish Balasubramian)表示:“模拟调谐意味着,考虑到整个系统的背景,您需要非常清楚地了解模拟电路的性能,这是您需要在硅中实现的。”“而这需要与你从硅中获得的相当接近。”

Mentor的首席科学家哈里·福斯特(Harry Foster)分析了威尔逊研究/Mentor调查的结果,看看这种激增是仅限于最新技术节点的设计,还是更广泛。事实证明,虽然7 nm或更低的波长是那些遇到这个问题的人最流行的答案,但它只占到了大约16%的情况。几乎所有的节点,包括150 nm和更大的节点,都出现了这种类型的故障。

第二个探索领域是这些问题是突然出现在大设计还是小设计上。结果可以在下面的图2中看到,但它清楚地表明,虽然所有设计规模都经历了与模拟调谐相关的问题的增加,但涉及最大设计的百分比最大。

图2:按设计大小调整模拟电路缺陷。资料来源:西门子旗下的Wilson Research and Mentor。

这个数字可信吗?Cadence高级产品经理Art Schaldenbrand表示:“跟踪模拟设计方法论进展的一种方式是,与其他元素相比,由于模拟设计的模拟元素而导致的现场故障百分比。”“在最近的一次VLSI测试研讨会上,有报道称95%的现场故障都是由于芯片设计的模拟元件造成的。模拟很难。模拟设计的挑战越来越难,模拟元素对设计的影响也越来越棘手。此外,模拟设计师面临的压力也越来越大。缩小模拟功率比缩小数字功率需要更多时间。这是因为我们必须重新设计我们在模拟领域所做的工作,以实现这一目标。“

各种规模和技术节点的设计都遇到了越来越多的模拟问题。“在两个主要领域的推动下,ASIC正变得越来越复杂,”Mentor的Balasubramian说。其中之一将是向高级节点的迁移。但最大的驱动因素是复杂混合信号设计的数量正在增加。这主要是由于公司试图优化区域占用面积,以便在同一技术节点中包括模拟。每个人都在试图迁移到单一的基底,或单一的技术节点。这本身就带来了很多挑战。当团队需要接触到模拟设计,或者需要接触到高级节点的一些效果时--比如更低的门槛,比如在寄生方面非常挑剔--他们不能做一个示意性仿真,然后说一切都正常。

该行业的一个重要增长领域来自物联网设备。Synopsys的模拟和混合信号应用工程经理Farzin Rasteh说:“当你关注移动、物联网或手持设备时,你会发现更多的模拟元件。”您将获得PLL、RF和高频调制电路。你会发现充电泵和运算放大器。而且所有这些设备都有传感器,本质上是模拟的。“。

新节点意味着更多问题。Fraunhofer IIS自适应系统工程部高级混合信号自动化组经理Benjamin Prautsch表示:“在最新的技术节点,有新的东西需要学习,完全理解它们并将这些新效应融入工具和模型需要时间。”“例如,在最新的节点,变异性很难建模。当许多根效果进入画面时,寄生提取变得困难得多,隔离依赖于布局的效果可能需要时间,这可能会加剧寄生问题。“。

其中一个新问题就是噪音。“台积电已经发表论文说,将模拟设计移植到更高的技术节点或先进的技术节点会带来它自己的挑战,”Balasubramian说。“最好的情况是一切正常,你可能很幸运。要做到这一点,你可能有很高的利润率。在大多数情况下,这将导致性能下降。但最坏的情况是它无法发挥作用。“。

当你把噪音和变化无常结合在一起时,情况会变得更糟。Synopsys的Rasteh说:“考虑一下电压调节器或电荷泵,它为数据路径提供电力。”“如果这里面有变化,如果上面有噪音怎么办?噪声如何在信号和时钟的计时中表现出来,进而可能导致故障?什么类型的因果关系存在,在这些小几何体上,在这些高频下,皮秒的每一小部分都很重要?这些都是通常会导致失败的事情。“。

有些问题会导致芯片失效,但可能需要重新旋转还有其他原因。Synopsys设计组的高级员工应用工程师Haran Thanikasalam说:“当涉及到变化时,最大的挑战是产量。”“我们依靠模拟来提供准确的基于西格玛的分析,这样他们就可以将其与产量下降联系起来。工具很难将不同的sigma值应用到电路的不同部分。因此,公司发出了测试芯片,这些芯片为各种分析提供了工具。他们可以推动硅的极限,然后在模拟和实际部件之间建立关联。“。

对模拟技术的期望更高,即使工艺技术正朝着相反的方向发展,改善模拟性能的压力依然存在。“有了芯片内集成,就不再有简单的模拟/数字边界,”Balasubramian说。他说:“我们看到这样的设计架构,模拟驱动数字的地方没有单向通信。取而代之的是反馈循环。考虑PLL的数字校准。锁相环过去是纯模拟的,但今天他们增加了数字校准,以使其更快、更容易收敛。现在,您的基本模拟模块有一个数字组件,它不再是单向流。这需要更先进的方法论。“。

拉斯特对此表示同意。“为了检查和调整,我们需要在设计中内置更多的智能。这可能包括带有反馈回路的自我控制,以监控这些事件的条件--无论是温度、接收到的信号功率、是否是错误检查机制、是否测量抖动或变化--以及自我校正和补偿。“

这增加了失败的可能性。Rasteh补充说:“可配置模拟已经变得非常流行。”“这是您使用数字或软件指示模拟转到高功率模式或高频模式、更改电流源的输出或更改电荷泵的输出的地方。设计必须对极端条件、天气变化或外部因素具有弹性,当您在如此小的区域中封装如此多的内容时,会受到高频电路、数字电路到模拟电路的串扰噪声,反之亦然。这并不容易模拟和建模。“。

推送性能所有的通信都依赖于模拟。至少会有串行设备驱动信号穿过恶劣的环境,而新版本的标准通常会对串行设备有更高的要求。“速度越快,精度就越高,”巴拉苏布拉米安说。“利润率越来越小,满足某些接口要求所需的速度意味着你必须考虑更多的物理影响。这在某些设计中并不容易实现,并且需要更多的调优。他们过去在签署模拟电路时甚至不考虑技术上发生的设备噪声。但是,设备噪音可能会增加到真正影响PLL性能的程度。“。

接口中非常小的错误可能会导致灾难性故障。Rasteh说:“工艺变化可能会在存储器的读/写过程中产生错误或延迟。”“如果与时钟边缘相差零点几皮秒,就足以使读写变得不可靠。如果每30或40个写入中就有一个是错误的,这就足以使芯片或内存控制器变得毫无用处。我们将这些问题归因于变异和更高的频率。因此,对抖动或任何错误的容忍度要小得多。工艺变化会在这些频率或时钟相位或抖动中产生更大的变化。而且因为在绝对时间上几乎没有余地,这些设计在变化下的反应更加明显。“。

更高的质量不仅速度加快,环境变得更加极端和嘈杂,一些市场也对质量提出了更高的要求。“任何用于汽车的芯片都需要极高的精度,”巴拉苏布拉米安说。“对于汽车行业来说,这意味着至少有5-sigma,可能还有6-sigma。在合理的时间内,他们不可能使用蒙特卡罗模拟来验证模拟电路。我们正在将机器学习技术引入变异分析。有了这一点,我们可以在有限数量的模拟中实现设备验证,而不是运行数十亿次模拟。“。

这需要在开发过程中做出改变。Synopsys的Thanikasalam说:“运行多个角(PVT)模拟永远不会发现变异问题。”“他们必须利用来自铸造厂的统计模型,他们需要扫除整个范围,才能捕捉到这些问题.”

前沿节点上的公司意识到了这一点。Fraunhofer的Prautsch说:“当过程和模型还在发展时,测试芯片就变得非常重要,可以成为验证提取的重要一步。”这些新的流程步骤很多都是从本质上非常手动开始的,在将重复性和/或容易出错的任务整合到工具中之前需要时间。

可以处理其中许多问题的工具正在合并。Rasteh问道:“一个工具怎么能识别出设计中对输出影响最大的部分。”“设计的哪个部分对错误的潜在影响最大?如果您有PLL,并且PLL上的抖动对您非常重要,那么控制抖动对您来说也很重要。那么,设计的哪些部分最有可能影响到这一点呢?它是压控振荡器,还是反馈回路,还是电荷泵?“。

结论虽然调查数字代表了需要模拟调谐的ASIC的极端跃升,但结果正确地识别了模拟设计在经历许多变化的过程中。那些处于极端边缘的人正经历着来自每个节点的持续的新挑战,并且他们相继变得更加复杂。可以对模拟进行调谐的测试芯片可能只是计划的一部分。

对于遗留节点上的设计,这些团队可能会被打乱,因为他们必须第一次处理集成问题。许多传统的方法,其中模拟和数字是分开设计和验证的,现在必须重新考虑,这会影响团队活力。

所有节点上的所有设计都被推向速度更快、功耗更低、产量更高的方向,而每一种设计都会逐渐增加复杂性。

相关Analog知识中心关于Analog的热门故事、特别报道、视频、博客和白皮书。7 nm及以上模拟设计中的问题和解决方案,以及在许多高级封装中,所有器件都会受到噪声和邻近效应的影响。为什么模拟设计会失败模拟电路很久以前就不再遵循摩尔定律了,但这并不总是有帮助的。当电压显著降低时,边缘设备的完整性问题在较老的节点上会成为一个严重的问题,这对于电池供电的设备来说是一个严重的问题。低功耗模拟随着数字电源的下降,模拟电路的耗电量越来越引起人们的关注,但模拟设计者几乎没有工具来帮助他们。

非常有趣的文章,谢谢布莱恩!几年前,我们在设计具有复杂模拟/混合信号、射频功能的下一代MCU平台时也面临着同样的挑战。很明显,我们需要在所有层次级别(包括模拟)进行正式的验证,并且我们提出了一种新的方法,使我们从5-10个体系结构错误(1p0到0个体系结构错误)中脱颖而出。诀窍是正式验证数字流中的每个IP,看起来它工作得很好,🙂