BladeRF-wiphy:开源IEEE 802.11兼容软件定义的无线电调制解调器

bladeRF-wiphy项目是一个开源IEEE 802.11兼容软件定义的无线电VHDL调制解调器。该调制解调器能够调制和解调802.11数据包(该协议基于WiFi协议),并可以直接在BladeRF 2.0 micro xA9的FPGA上运行。

与Linux mac80211结合使用的bladeRF-wiphy使bladeRF 2.0 micro xA9成为软件定义的无线电802.11接入点! 802.11数据包(PDU)直接在FPGA上进行调制和解调,因此仅802.11数据包在FPGA和libbladeRF之间传输。

注意:虽然JTAG适配器(USB-Blaster)可以帮助您在运行时了解调制解调器,但是运行下面链接的RBF并不需要JTAG适配器。

有关编译,安装和运行bladeRF-wiphy的说明,请参阅bladeRF-wiphy说明。要模拟bladeRF-wiphy模拟,请参阅bladeRF-wiphy模拟指南。

虽然用HDL来实现调制解调器比完全用C或Python编写的调制解调器要困难得多,但HDL和FPGA允许调制解调器开发的最关键方面之一:低延迟和定时控制。

在IEEE 802.11中,特别要求接收调制解调器(无论是客户端STA还是接入点AP)必须通过在接收到的调制解调器的10微秒内开始发送ACK数据包来确认已成功收到寻址到它的传入数据包。传入数据包的末尾。这是不切实际的,或者有时根本无法用C和Python软调制解调器满足如此狭窄的时序要求,因为数据总线在流原始IQ样本所需的带宽上具有相对较高的延迟。如果IQ样本必须通过总线发送,由CPU处理并通过同一总线发送回响应,则即使是PCIe和USB等高速总线也会增加太多延迟。与HDL调制解调器相比,这种情况不太理想,在HDL调制解调器中,开发人员对调制解调器中的信号的延迟和定时具有完全确定性和“时钟周期精度”的控制。 HDL调制解调器还受益于可以在FPGA中实现的大规模并行化。在这种情况下,控制和性能水平使HDL调制解调器具有独特的能力,能够处理在10微秒内生成ACK响应的任务。

值得注意的是,精益HDL调制解调器倾向于在其DSP管道中使用定点算法,这与用C,Python等编写的软调制解调器形成鲜明对比,后者大多使用浮点算法来受益于AVX等加速器(在CPU)和GPGPU。这种加速器工具箱的一个示例是GNURadio Volk(https://github.com/gnuradio/volk)。 HDL调制解调器中定点算法背后的主要驱动力是FPGA中浮点算法相对大量的逻辑资源利用率。

Warning: Can only detect less than 5000 characters

以下各小节的名称主要对应于BladeRF-wiphy的fpga / vhdl目录中的模块。

wlan_top模块实例化了BladeRF-wiphy IEEE 802.11兼容调制解调器的三个核心组件,包括RX,TX和DCF模块。 DCF模块会不断确定当前调制解调器是否愿意进行传输。根据发射机要发送的数据包类型,它必须等待短帧间间隔(SIFS)或DCF帧间间隔(DIFS)所指定的时间。 IEEE 802.11调制解调器必须针对寻址到它的每个接收到的帧以应答(ACK)帧进行响应。定义为SIFS的硬限制要求ACK帧的传输从接收到的帧结束的10微秒开始。在SIFS时间内,其他接收原始帧的IEEE 802.11调制解调器知道给预期的接收者时间来生成ACK数据包。但是,如果当前调制解调器由于具有数据帧或管理帧而要发送,则它必须等待定义为DIFS的时间后才能发送。最初,DIFS在20到50微秒之间,但是如果无法访问该介质,则由于指数退避算法,等待时间可能成倍增长至几毫秒。 wlan_top的RX状态机等待来自wlan_rx的解码数据包,并将其转换为标准的packet_control_t接口,以便通过libbladeRF交换数字有效负载。万一wlan_rx内核确定需要发送ACK帧,它将使用必须接收ACK数据包的原始发送器的MAC地址声明ack_mac和ack_valid。 wlan_top的TX状态机等待DCF告知它何时可以发送。如果有任何ACK数据包,则TX状态机在发送之前会等待SIFS时间。但是,如果要传输任何其他类型的数据或管理帧,则TX状态机将等待DIFS设置的时间。

如果调制解调器确实有要发送的东西但介质(RF通道)当前很忙,则DCF实施指数退避算法,该算法连续等待的时间最多是前一个等待时间的两倍。指数补偿的思想是避免多个发送器之间出现争执,因为许多被阻止的发送器由于介质再次可用而同时注意到它们可以发送信号。此过程称为载波侦听多路访问/冲突避免(CSMA / CA)。

wlan_tx_controller模块是传输链中两个主要状态机的主要模块。它的主要目的是在启动wlan_framer模块之前生成前同步码并等待其完成。标准802.11帧的前导码由10个短训练序列(STS)和一个0.8微秒的循环前缀(CP)组成,用于两个3.6微秒长的长训练序列(LTS)。 wlan_tx_controller断言short_start以启动STS,并等待long_done,然后断言encoder_start以启动wlan_framer模块。启动wlan_framer之后,wlan_tx_controller等待指示数据包已完成调制的指示。

wlan_framer模块主要负责接收PDU字节并将其发送到调制器。在生成完前同步码之后,wlan_framer立即接收对传输链的控制。 wlan_framer生成的第一个符号是SIGNAL符号。该符号基于tx_vector,tx_vector是元数据HDL信号,它通知调制器PDU有多长时间及其预期的传输MCS。 SIGNAL符号解码为3个字节,这3个字节包括确定数据包长度的字段以及以下OFDM符号的调制和编码方案。应当注意,SIGNAL符号始终以6Mbps的速率进行调制。

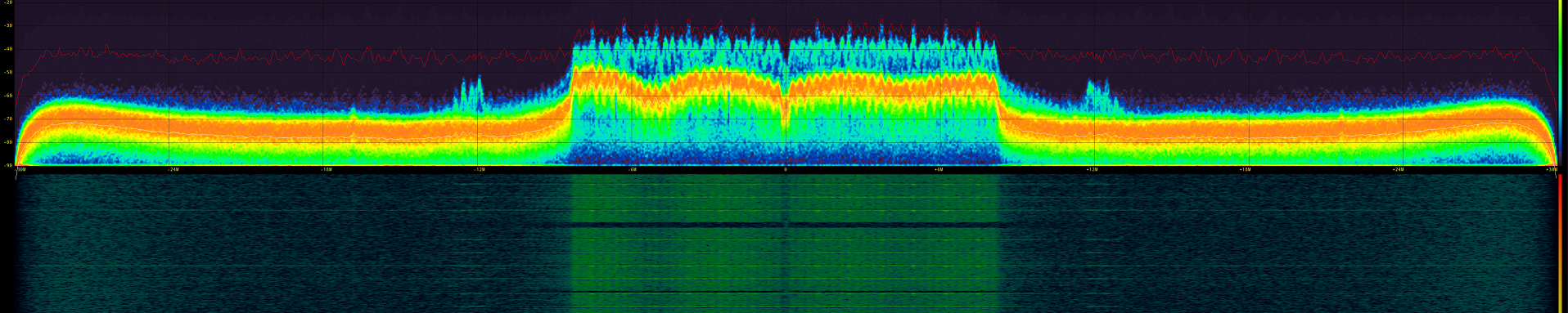

为了透视输出中最终目标wlan_tx_controller和wlan_framer试图达到的目的,下面是典型IEEE 802.11突发的图示。典型的脉冲串包括前同步码(接收器用来估计符号定时,中心频率偏移和信道脉冲响应)和数据符号(第一个是SIGNAL符号,其后是直接编码有效负载的符号)数据)。框图下方显示的绿色波形是wlan_tx生成的示例IQ样本。

wlan_framer状态机准备足够的字节以一次生成一个OFDM符号。分派了足够的字节后,它等待断言mod_done,以便它可以准备下一个符号。 wlan_framer使用CRC多项式在PDU的末尾附加32位CRC:CRC:CRC多项式= x ^ {32} + x ^ {26} + x ^ {23} + x ^ {22} + x ^ {16} + x ^ {12} + x ^ {11} + x ^ {10} + x ^ 8 + x ^ 7 + x ^ 5 + x ^ 4 + x ^ 2 + x ^ 1 + x ^ 0

每个PDU字节通过XOR操作与相应的LFSR值一起加扰。 wlan_scrambler模块使用wlan_lfsr模块为每个PDU字节生成相应的LFSR值。 SIGNAL符号未加扰。每个OFDM符号需要固定数量的字节进行调制,如果PDU的长度不足以填充最后一个符号,则wlan_scrambler会创建尾随零以填充最后一个符号,直到调制器模块有足够的字节来对其进行调制。

wlan_encoder模块根据从wlan_scrambler接收到的加扰字节生成卷积编码器编码位。 wlan_encoder在每个符号的字节数上工作,类似于wlan_scrambler。 2码卷积编码器将为接收到的每个未编码位产生2个编码位,从而赋予其“半速率”,r = 1/2。 IEEE 802.11要求更多速率,包括r = 2/3和r = 3/4,这些速率通过确定性地擦除编码位来实现,例如在r = 3/4速率的情况下,每3个未编码位擦除一次如果将其呈现给编码器,则将2个比特删截(或擦除)并发送4个比特。只要发射器和接收器都知道擦除发生在哪里,就可以通知接收器的维特比解码器忽略那些丢失的编码位。去除编码比特以降低纠错为代价,提高了吞吐量(由于有效地减少了冗余)。这就是为什么更快的MCS具有更高的编码率的原因之一,该规范假设已经有足够的SNR来传输像64-QAM这样的高阶调制,因此假定较低的错误保护率就足够了。

为了避免分组的位错误簇,使用交织来分离相邻位。如果某种信道障碍通过交织破坏了OFDM符号的一部分,则编码比特很可能不相邻。比特错误的这种分布然后允许维特比解码器在网格长度的一部分上潜在地校正一些比特错误。根据IEEE 802.11中建立的模式对比特进行交织。

wlan_modulator模块开始通过称为调制的过程将数字位转换为IQ样本的过程。 wlan_modulator基于数据包的相应调制方案,将来自wlan_interleaver的编码位转换为星座点。 IEEE 802.11规范要求对OFDM速率进行几种调制,包括BPSK,QPSK,16-QAM和64-QAM。发送到wlan_modulator的编码位用作星座图中每个相应调制的索引。选择IEEE 802.11 OFDM具有48个数据承载子载波,并且所有子载波具有相同的调制方案。在6Mbps速率的情况下,子载波经过BPSK调制,这意味着每个子载波仅将1个编码位调制为BPSK。在这种情况下,wlan_modulator使每个子载波中的1位出队,并使用该1位编码的位作为索引对应于BPSK调制的查找表,例如(-1表示0位,+ 1表示1位)。类似地,作为另一个示例,54 Mbps的速率使用64-QAM作为其调制,这意味着每个子载波需要6个编码位才能索引64-QAM的星座映射。对于48个数据子载波,wlan_modulator需要48个数据子载波中的每个6个编码位,每个OFDM符号总共288个编码位。

一旦wlan_modulator将编码后的比特调制为星座点,即可通过简单的逆FFT将IEEE 802.11 OFDM中的复数(具有实部和虚部)星座点转换为复杂的IQ样本。在全部64个子载波(不久将称为FFT仓)上执行逆FFT,其中包括4个导频音,48个数据子载波,1个DC仓和9个零仓,它们有助于缩小IEEE 802.11频谱旁瓣。

wlan_ifft64生成原始基带IQ样本,该样本被发送到DAC以转换为模拟信号。 IEEE 802.11符号的长度为4微秒(假设较长的保护间隔),但是以20MSPS采样的64个IQ样本仅为3.2微秒。剩下的0.8微秒用作符号之间的间隔,以减少符号间干扰(ISI)。精确对应于20MSPS时的16个IQ样本的0.8微秒间隙位于每个OFDM符号周期的开始处。但是,间隙不是空白,而是将逆FFT输出的最后16个样本复制到OFDM符号的开头。间隙中的样本称为循环前缀(CP)。由于傅立叶变换每2 * \ pi循环一次,因此在CP的末尾与由逆FFT生成的64个样本的开始之间,相位是连续的,在这种情况下2 * \ pi是64个样本。

wlan_sample_buffer模块还用于为两个背对背的长训练序列重复创建32个样本(1.6毫秒长的循环前缀)。

wlan_tx_short模块生成定义IEEE 802.11简短训练序列的16个样本。 STS阶段为8微秒长,旨在帮助任何接收器锁定其自动增益控制(AGC),并获得数据包的大致时序估算; wlan_rx模块涵盖了该主题。

wlan_tx_long模块生成定义为IEEE 802.11长训练序列的64个样本。 LTS阶段也为8微秒长。该序列旨在估计中心频率偏移,并作为生成初始均衡器参数的参考。 wlan_rx模块涵盖了该主题。

为了确保调制解调器能够尽快处理接收到的RX样本,wlan_rx模块的一部分以4倍于采样率时钟速率(20 MSPS)的速率运行。因此,大多数OFDM接收器有效地在80MHz时钟域中运行,并且需要自己的PLL。

当检测到突发时,此模块会通知调制解调器的其余部分。一系列高能量IQ样本通常表示一个数字数据包。编写该模块是为了允许BladeRF-wiphy调制解调器控制手动增益控制或解释AGC的信号。如果使用bladeRF 2.0 micro xA9,则当AD9631锁定到ADC时,可以使用AD9361的物理控制GPIO引脚(adi_ctrl_out(0))通知调制解调器。

......