奇怪的芯片:老式IBM令牌环控制器的拆卸

IBM在集成电路中使用了一些不寻常的技术,最明显的方法之一是将它们包装在方形金属罐中。由于没有太多关于它们的信息,我最近一直在研究这些芯片。打开了大型金属芯片-1.5"从下面的令牌环网络板的侧面看。该芯片结合了模拟电路,定制微处理器和complexlogic,结果比我预期的更奇怪,更有趣。内部封装也不是常规的:代替使用的键合线由大多数制造商来连接硅芯片,IBM使用了“倒装芯片”。技术,将芯片倒置焊接到陶瓷基板上。芯片的表面上没有焊球,而不是焊盘,这给它带来了意想不到的布局和外观。在博客文章中,我将详细讨论该芯片。

IBM 4/16 ISA令牌环板。单击此照片(或其他任何照片)获得更大的版本。

令牌环网络由IBM于1985年推出,1是一种与以太网和其他网络系统竞争的局域网技术。将它们传输到环路中的下一台计算机。为使计算机能够访问网络,在环中循环了一个特殊的三字节令牌。当计算机收到令牌时,可以将网络数据包传输到环路中的下一台计算机。数据包绕环行进,直到返回原始计算机。该计算机丢弃该数据包并在其位置发出令牌,从而使另一台计算机有机会传输数据。如果两个令牌同时发送,则会检测到冲突,然后稍后再试。令牌环网络的优势是避免冲突,使其更具确定性和公平性,并在拥塞的网络上提供更好的性能。

IBM对方形金属罐的使用可以追溯到1960年代初,当时使用IBM的SLT模块(固态逻辑技术)。因为IBM当时认为集成电路不够成熟,所以他们使用小型混合模块。在陶瓷基板上安装了一些晶体管,二极管和电阻器。这些半英寸见方的SLT模块封装在铝罐中进行保护,从而使IBM电路板具有独特的外观。在1960年代后期,IBM转向了集成电路。 2,但他们保留了½"金属罐代替了其他制造商使用的矩形陶瓷或环氧树脂包装。由于集成电路需要更多的插针,IBM增大了包装尺寸,从而导致体积过大的1.5"我检查过的包裹。

为了检查集成电路,我用热风枪将其从板上卸下。在下面的照片中,您可以看到芯片下面的引脚网格。芯片标记为部件号为50G6144。防静电后缀表示静电敏感设备,该设备可能会被静电损坏并需要特殊处理。下一行IBM 9352PQ是制造工厂的代码。最后一行194390074M表明该芯片于1994年第39代生产。一年中的一周。

切掉铝盖露出内部的硅片。芯片倒装安装为倒装芯片,直接焊接到陶瓷基板上的连接处。因此,您看不到芯片电路,仅在硅芯片的下面即可。IBM称这种安装技术为可折叠芯片连接或C4。 3(相比之下,大多数制造商将硅芯片的右侧向上安装,并用细小的键合线将其连接到引脚。)细小的印刷电路走线将模块的175引脚连接到芯片。

去除金属盖的集成电路,显示了陶瓷基板上的硅芯片。

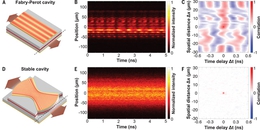

我用热风枪从基板上移出芯片,然后用过氧化氢和醋的混合物溶解焊球。用金相显微镜拍摄大量照片,我在下面创建了芯片照片。是焊球的位置,比您预期的更不规则,它们不在管芯的边缘(如焊盘),但与电路重叠,芯片相当大,约为9×7.9 mm,具有特征大约为1μm。注意电路的水平行;这些是标准单元格,我将在下面讨论。

芯片的照片。单击此(或任何其他)图像以获取较大的版本。

焊球的图案在下面的Antoine Bercovici的照片中更清晰可见。在四个侧面上有三排深的焊球,从芯片中间排成一排,在角部则更多。边缘的焊球用于发出信号,而中间的焊球用于分配电源和接地。请注意将焊球连接到底层电路的芯片顶部缠结的金属布线。 4

模切照片清楚地显示了锡球和上部金属。由Antoine Bercovici提供,此处为全尺寸版本。

下图显示了固定模具的陶瓷基板的特写;将图案与上面的模具进行比较。 5芯片被焊接到中间的矩形触点阵列中,而照片边缘周围的大圆圈是芯片的引脚,请注意引脚和细小的触点之间的密集,复杂的布线图案,布线痕迹极其明显薄(约30µm),电源和地面走线更粗。触点形成复杂的图案。大多数以矩形阵列排列,深三个。但是,通过芯片中心还有成排的触点,与电源交替连接并通过矩形内的粗迹线和一些分散的触点进行接地。针对该特定芯片的布局,优化了基板上的触点图形。功率分配是一个特别需要考虑的问题。

考虑粗略的0.1"之间的连接层次结构很有趣。芯片引脚的网格和芯片上1μm的微小特征。在顶层,引脚间距为0.1英寸。在14×14的网格中,焊球的间距为0.01&#34 ;,因此陶瓷基板将间距减小了10倍。焊球连接到管芯顶部的布线,间距为0.001 &#34 ;,将密度增加另一个10倍。顶部布线连接到芯片上的基础布线,间距为0.0001&#34 ;,另一个10倍。最后,裸片上的特征尺寸约为1µm,是另外2倍。

使用这种类型的封装,您可以通过观察IC的下侧(下图)来可视化管芯的位置。由于芯片是直接焊接到基板上的,所以没有引脚可以固定在芯片上。因此,没有引脚的斑点指示管芯的位置。

下图显示了溶解了大部分金属层的芯片,使得下面的晶体管结构可见。该芯片具有三个主要组件:一个16位微处理器CPU,一个用于网络信号的模拟前端以及用于24,000个逻辑门的该芯片的左侧还具有一些缓冲RAM,中间和底部具有I / O驱动程序。(IBM最初使用6个模拟和数字芯片实现了令牌环接口,为降低成本,他们将所有功能都投入了集成到单个芯片上,从而实现模拟和数字电路的结合。)

标有主要成分的模具。金属层已被移除,以显示其下方的电路。

下面的框图显示了芯片的复杂功能,从右上角开始,模拟前端电路与环网通信。模拟前端从网络信号中提取时钟和数据。协议处理程序实现了底层令牌环协议:解码数据,将数据包分解为帧并执行错误检查。网络数据通过共享RAM控制在片内缓冲区和外部RAM之间移动。最后,一个定制的16位微处理器实现了数据链路层协议并控制芯片。

该芯片的逻辑由CMOS标准单元库实现,由大约24,000个门组成。标准单元逻辑的思想是每个功能(例如NAND门或锁存器)都具有标准布局。然后由自动化设计工具组合以创建所需的逻辑(这与较早的方法相反,在以前的方法中,设计人员会在纸上或使用设计软件分别对每个晶体管进行布局。)由于采用了软件,标准单元使芯片设计更加容易可以进行电路综合,布局和布线,但是设计不像完全定制的电路那样灵活或优化。

标准单元布局在芯片上可见,单元以均匀的行排列,并通过水平和垂直布线连接。下图放大了管芯以放大五行标准单元逻辑,然后放大一行显示细胞在芯片上的大小。

放大裸片可显示标准单元逻辑的行。另一个缩放显示该逻辑的详细信息。

下面的标准单元实现了3输入NAND门,Ill将解释其构造方法。 6顶部有6个PMOS晶体管,底部有6个NMOS晶体管,这些晶体管由顶部的掺杂硅区域和底部的另一个硅区域形成,多晶硅的垂直线(一种特殊类型的硅)形成晶体管的栅极。多晶硅也用于电池内部的垂直布线。芯片具有三层金属:底层用于水平布线,中间层用于垂直布线,顶层连接到焊球。连接电池内部的晶体管并将电池与其他电池连接。两条粗水平金属线为电池提供电源和接地;第二层垂直金属层提供跨电池和电池之间的垂直布线。该层还实现了电池之间的电源连接焊球和水平电源线在此处可见。圆点是各层(硅,多晶硅或金属)之间的连接。 细胞。

在下面的示意图中,我已移除了冗余晶体管并重新布置了布局,以使NAND电路更加清晰。如果所有输入均为1,则底部的NMOS晶体管将导通,将输出拉低。 0时,PMOS晶体管导通,将输出拉高。因此,该电路实现了与非门。

总而言之,标准单元逻辑提供了一种方便,自动化的逻辑实现方式。少量标准化单元实现了基本逻辑功能。这些单元排列成行并连接在一起以创建所需的逻辑。(从拆解的角度来看,标准单元逻辑有些令人失望,因为高级结构不可见;它只是一堆统一的单元)

逻辑电路包括一些静态RAM缓冲区,用于保存网络数据。这些是自定义实现的(与I / O驱动程序一样),而不是使用标准单元。下图显示了一块RAM单元。

该芯片包含一个由IBM 7定制设计的16位CMOS控制微处理器,并包含大约10,000个门。该处理器处理网络协议,控制发送和接收操作以及管理共享内存,其运行频率为5.34兆赫,执行3 MIPS(每秒百万条指令)。微处理器从板上的EPROM运行代码。 IBM将其称为“微代码”,但目前尚不清楚这是通常意义上的微代码还是仅仅是固件说明。

CPU是用标准单元逻辑构建的(RAM和ALU除外),但是奇怪的是,单元布局与芯片的其余部分完全不同,可能是因为它的设计者不同。下图比较了CPU逻辑(左)与另一个逻辑(右).CPU在容纳4行常规逻辑的同一垂直空间中容纳了7行逻辑,另一方面,右侧的逻辑似乎在水平方向上非常密集。

以相同的比例比较CPU的标准单元逻辑(左)与芯片的其余部分(右)。

在裸片上可见的CPU的一项设计功能是它使用多个PLA(可编程逻辑阵列)进行指令解码和控制。(看照片,我在角落看到了9个小型PLA和一个大型PLA。 PLA提供了一种结构化且密集的方式来实现逻辑(通常是AND-OR逻辑)。更重要的是,PLA还提供了灵活性和轻松更改设计的能力。在下面的PLA中,左下角输入了12个信号。上面的矩阵将这些信号转换为向右传递的11个信号。第二个矩阵生成8个输出。 PLA的内容以金属层中的图案可见。由于可以通过更改芯片的金属层来修改PLA,因此甚至可以在蚀刻硅之后进行错误修复。

CPU包含用于寄存器存储的存储单元(它们称为16×16高速缓存)。此RAM设计与逻辑电路中的RAM设计不同。

该芯片包含以CMOS形式实现的模拟电路块,该电路执行信号转换和时钟恢复功能,以及检测和补偿线路损伤,该电路包括电阻器,电容器,具有特殊特性的MOS晶体管,以及其他组件。 8模拟模块使用各种电路,例如运算放大器,开关电容器放大器,参考电压,峰值检测器,电荷泵,压控振荡器和锁相环。

设计中的一项挑战是最大程度地减少抖动。从网络数据提取的时钟信号中,由于每个节点都重新传输了数据,因此当数据包穿过环时会累积抖动,因此每个节点都必须是准确的,他们使用了多种技术来防止噪声进入信号中,例如为模拟电路提供单独的电源和地,使用电路中的差分信号,并使逻辑信号远离模拟电路。

模拟电路使芯片的制造和测试变得更加复杂。 9电容器和特殊晶体管在制造过程中需要特殊的处理步骤。制造公差也要严格得多,因为处理变化可能会改变电气特性,足以使模拟电路停止工作。有些模拟电路过于敏感,无法在晶圆上进行测试,因此无法#39;直到封装好芯片后才进行测试,使失败的芯片变得更加昂贵。即使如此,IBM还是值得在芯片上放置模拟电路的。

IBM最初是在1988年制造令牌环芯片的。我检查的芯片是1994年的较小版本。注意,两个芯片具有相同的微处理器模块(左上角)和相同的模拟模块(左下角/右上角)。左侧的焊球连接到底层电路,而右侧的焊球通过第三层金属布满整个芯片。

旧芯片的模拟部分被原样复制到新芯片上,但与焊球的连接却大不相同,显示了接线技术的变化。在旧芯片(左)中,焊球位于金属焊盘的上方连接到电路。布局类似于使用引线键合和键合焊盘的集成电路,在旧芯片(右)中,焊球栅并没有固定在底层芯片架构上,而是遵循其自身的约束,新的金属层连接了焊球到垫子上。尽管未在新芯片中使用过,但焊盘仍保持其原始位置。

比较旧芯片和新芯片的模拟部分。芯片的颜色因照明而异。

我只说说包含该芯片的令牌环板。该板是1994年的ISA卡.IBM芯片在该板中占主导地位,但也有许多其他芯片,主要是74F系列TTL。 #39;也是方形的(而且奇怪的是厚的)莱迪思芯片,可能是GAL(通用阵列逻辑).GAL是一种可编程逻辑芯片,将AND / OR逻辑与触发器结合在一起.Signetics芯片上贴有IBM标签顶部可能是现场可编程逻辑阵列(FPLA)。尽管IBM芯片非常复杂,但该板仍需要大量可编程逻辑和简单逻辑IC,主要是与计算机的ISA总线接口。用于存储网络数据的64 KB RAM,两个Toshiba TC55329 32K×9位静态RAM芯片。该RAM可通过网卡和主机PC访问。内部微处理器的代码包含在板上的EPROM芯片中,这是一种AMD 128C 27芯片,可容纳128 KB 16位字。EPROM芯片上带有不干胶标签,带有t IBM部件号73G2042,指示微码版本。

电路板的右侧装有模拟电路,用于与网络连接。五个脉冲变压器在接口板和网络的潜在危险电压之间提供电气隔离。两个不使用的旁路继电器可将卡从环上断开,保持环的连通性。还有两个晶体管阵列以及电阻器和电容器,用于在将网络信号传递到令牌环芯片之前对网络信号进行调节。该卡通过RJ-45连接器连接到网络,可以使用该连接器带有非屏蔽双绞线(UTP)电缆。背面还有一个DB-9连接器,可与屏蔽双绞线(STP)一起使用。 11

在1980年代,许多不同的局域网络进行了竞争,包括以太网,令牌环,Datapoint的ARCnet,AppleTalk,Omninet和Econet。到1990年代初,以太网由于多种因素而获胜:成本低得多(大约1令牌环成本的/ 5),更低的复杂度导致更快的技术改进(例如100 Mb / s以太网和交换式以太网)以及比IBM提供的范围更广的生态系统。 10芯片的复杂性反映了令牌环的复杂性,并说明了1980年代IBM的技术优势是一把双刃剑:尽管它最初给令牌环带来了巨大的性能优势,但更简单的以太网技术最终获得了胜利。 12

IBM徽标以及神秘的代号" PINEGR SH"位于模具的左下角。

感谢Antoine Bercovici提供的照片和信息。感谢我的Twitter读者进行讨论。我在Twitter上发布我的最新博客文章,所以请关注我@kenshirriff。我也有一个RSS feed。

IBM的令牌环网的灵感来自1970年代的环网研究,例如Cambridge Ring。 ↩

下图说明了芯片上焊球的复杂结构,将薄薄的铝,铬,铜和金层放在硅上以获得所需的性能,然后再一层铅锡焊料进行回流铬与氧化层结合,而铜提供可焊性,而金则保护铜不被氧化。

芯片顶层的金属布线看起来很乱,但后面有一些结构,下图显示了该布线的一小部分,用彩色表示了结构,焊球以黄色表示。 红色和蓝色走线通过芯片上的焊球传输功率和接地,这些走线与垂直布线的金属线连接,从而在整个芯片上传输功率和接地,另一条布线将信号焊球连接到I / O驱动器 ,收敛于g的窄带 ......