IBM创建了第一个2nm芯片

每十年都是测试摩尔定律限制的十年,这十年没有什么不同。随着极端超紫(EUV)技术的到来,现在可以使用EUV提供的更精细的分辨率来应用于先前技术节点上开发的多地位技术的复杂性。除了其他更多的技术改进之外,可以导致晶体管大小的减少,从而实现半导体的未来。为此,今天IBM正在宣布它创建了世界上第一个2纳米节点芯片。

只是为了在这里澄清,而过程节点被称为“2纳米”,则没有任何关于晶体管尺寸的尺寸,类似于传统期望2nm可能是什么。在过去,芯片上的尺寸是芯片上的2D特征大小的等效度量,例如90nm,65nm和40nm。然而,随着3D晶体管设计的出现,使用FinFET等,过程节点名称现在是“等效2D晶体管”设计的解释。

该芯片上的一些功能可能是实际纳米中的低单位数字,例如晶体管鳍漏保护层,但重要的是要注意如何在当前命名的过程节点中的断开连接。通常,参数枢转到晶体管密度作为更准确的指标,这是IBM与我们共享的东西。

今天的宣布指出,与现代7NM处理器相比,IBM的2NM开发将以相同的电源或75%的能源在相同的功率下提高45%,或者在相同的性能下。 IBM热衷于指出,它是第一个在2015年和2017年展示了7米的研究机构,其中后者从FinFET升级到纳米片技术,允许更好地定制各个晶体管的电压特性。

IBM指出,该技术可以将500亿晶体管合适到指向指甲尺寸的芯片上。我们致电IBM要求澄清指甲的规模是什么,因为内部我们正在提出50平方毫米至250平方毫米的数字。 IBM的新闻关系表示,此上下文中的指甲是150平方毫米。将IBM的晶体管密度为每平方毫米(MTR / MM 2)为33300万晶体管。

正如你所说,不同的铸造厂有不同的官方名字,具有各种密度。值得注意的是,对于晶体管库,这些密度数通常被列为峰密度,其中模具区域是峰值问题的,而不是频率缩放 - 由于功率和热关注,处理器的最快部分通常是致密的一半。 。

关于移动到门 - 全部/纳米片晶体管的运动,同时没有通过IBM明确说明,图像显示该新的2NM处理器使用三堆GAA设计。三星正在3nm介绍Gaa,而TSMC则等待2nm。相比之下,英特尔将相信,将在5纳米流程上引入某种形式的Gaa。

IBM的3堆GAA使用单元高度为75nm,电池宽度为40nm,并且各个纳米片的高度为5nm,彼此分开5nm。栅极多间距为44nm,栅极长度为12nm。 IBM表示,它的设计是第一个使用底部基代隔离通道的设计,它能够实现12nm的栅极长度,并且其内部间隔物是第二代干工艺设计,有助于实现纳米换句的开发。这是通过在工艺的Feol部分上的EUV图案上的首次使用,使EUV能够为临界层的所有阶段提供EUV。

用户可能会想知道为什么我们听到IBM是第一个2nm芯片。 IBM是世界上未来半导体技术的领先研究中心之一,尽管没有铸造出自己的铸造产品,但IBM与其他人一起与其制造设施合作开发知识产权。 IBM将其制造业销售给2014年的10年伙伴关系的全球化,IBM目前还与三星合作,最近宣布与英特尔合作。毫无疑问,后两者将与IBM围绕这一新发展的一些级别合作,以获得自身生产链的可行性。

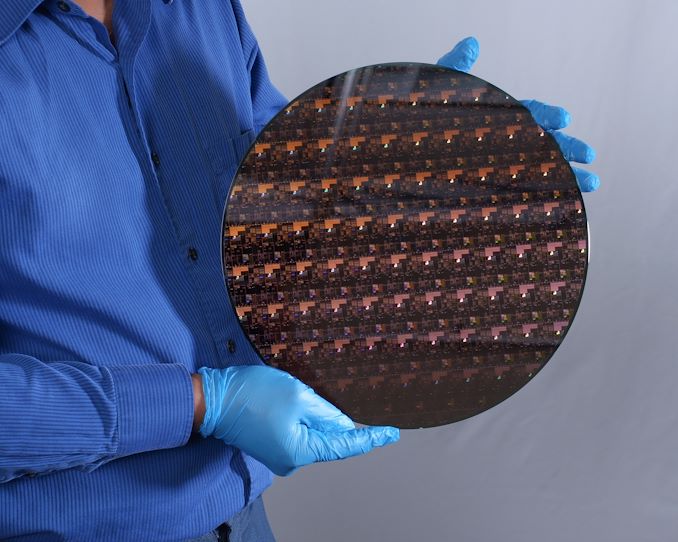

没有提供2nm测试芯片的详细信息,尽管在此阶段,它可能是具有较小逻辑的简化SRAM测试车辆。 12英寸晶片图像展示各种不同的光衍射,这可能指向各种测试用例,以确认该技术的可行性。 IBM表示,测试设计使用多VT方案进行高性能和高效应用演示。

该芯片于IBM的奥尔巴尼研究设施设计和制作,配备了100,000平方英尺。洁净室。该设施的目的是建立在IBM的广泛专利和许可投资组合,以便与合作伙伴合作。

我们有一系列有IBM专家等待回应的问题。我们现在还有积极的邀请,何时可以再次旅行。

发表评论非常好奇,在真正的吸气芯片中看到Gaa,如果它与看起来一样大量的改善。可能不是密度而且性能和功耗。我也不确定我是否从三星达到它,但它比FinFET更好地缩放/ perfroms,这尤其比FinFET更好?这将是一个巨大的优势!回复