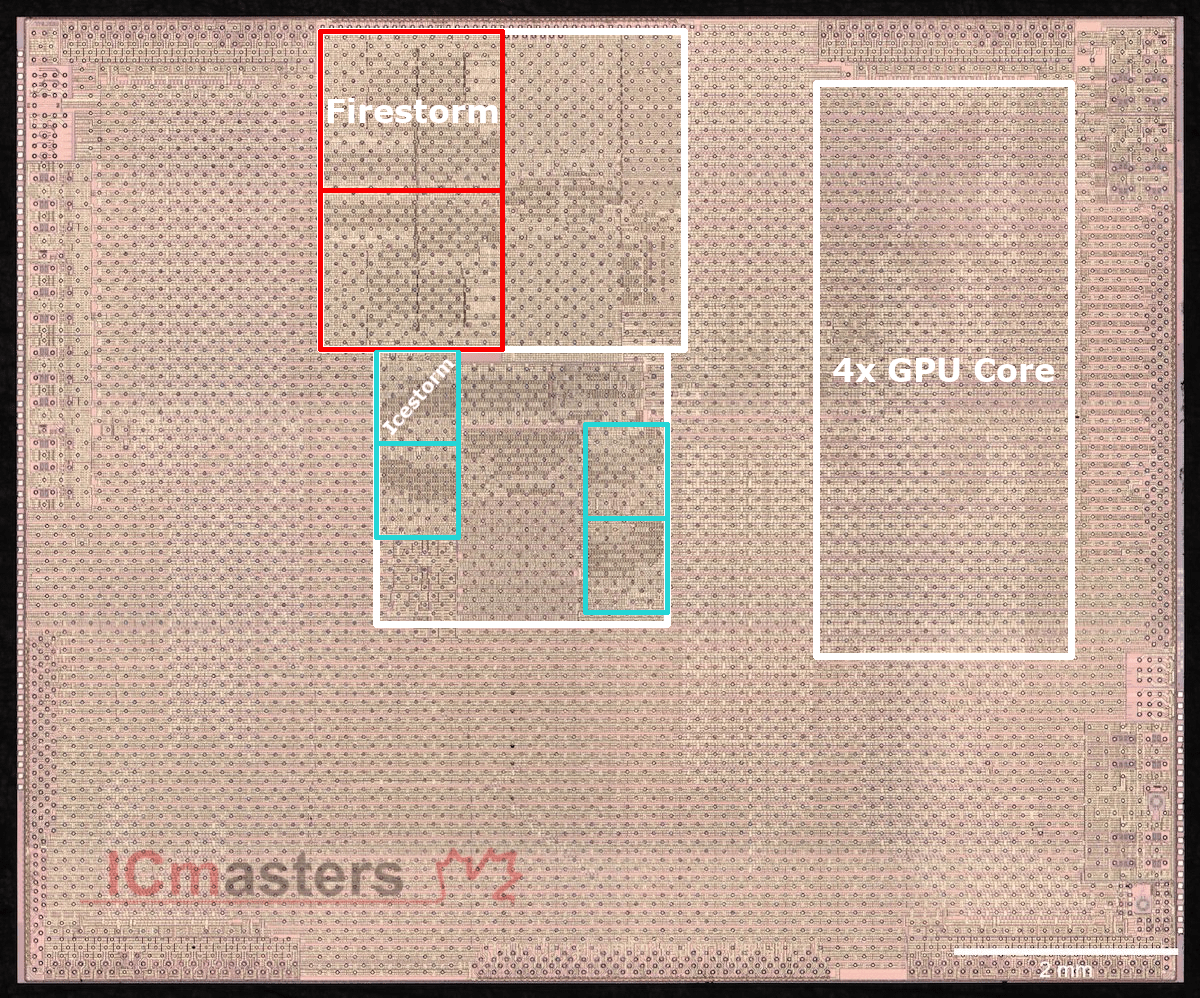

Apple的A14封装134M晶体管/mm²

2020-10-28 04:18:08

我们在ICmaster的朋友们已经深入研究了苹果A14仿生的包装。芯片尺寸已经被揭开,达到88mm2。尽管塞入了118亿个晶体管,但由于采用了台积电的5 nm工艺节点,芯片尺寸非常小。

进步的进程并非一帆风顺。苹果的芯片历来在其处理器中达到了工艺节点理论密度的90%以上。这一代人之所以脱颖而出,是因为他们在很大程度上错过了这一标志。与理论密度相比,A14的有效晶体管密度高达78%。尽管台积电声称N5缩小了1.8倍,但苹果只实现了1.49倍的收缩。

这并不是因为台积电或苹果的失败。这两家公司分别是半导体制造和设计的明显领先者。相反,这种将理论密度转换为有效密度的失败源于SRAM缩放的缓慢消亡。从寄存器到高速缓存,SRAM在整个处理器中被广泛使用。台积电(TSMC)的杰弗里·耶普(Geoffrey Yeap)声称,典型的移动SoC由60%的逻辑、30%的SRAM和10%的模拟/IO组成。

台积电的N5节点显示出SRAM伸缩放缓的迹象,与之前的收缩有所不同。尽管SRAM在逻辑上是完全缩小的,但它是1.35倍的缩小。这个数字被夸大了,因为一旦考虑到其他辅助电路,它最终会更低。SemiAnalysis预计这将是一种趋势,并将在新节点中持续存在。台积电和三星已经在展示3D堆叠式SRAM,这将有助于缓解密度问题。

3D堆叠不是灵丹妙药。成本增长已经开始大幅放缓。随着台积电N5晶片定价在约17K美元的范围内,很明显,每个晶体管的成本并没有下降。即使SRAM的规模保持不变,从N7到N5,每个晶体管的成本也将保持不变。