英特尔Xe-LP GPU架构深入研究

作为今天英特尔架构日的一部分,英特尔花了大量时间谈论公司的GPU架构计划。虽然英特尔本身并不是一个害羞的地方,但该公司最出名的仍然是它的CPU内核,因此他们在图形业务方面投入的营销注意力一直比较弱。但是,就像英特尔的其他许多事情一样,时代在变化-英特尔不仅在GPU上投入了越来越多的资金,而且在接下来的两年里,他们将过渡到PC GPU领域真正的第三方,推出几代人以来的第一款新的独立GPU。

作为英特尔之前宣布的Xe GPU架构的一部分,该公司打算成为一家自上而下的GPU提供商。这意味着为从数据中心和HPC群集到高端游戏机和笔记本电脑的一切提供离散和集成的GPU。对于一家在过去十年里只提供集成GPU的公司来说,这是一次大规模的扩张,而且需要大量的工程技术才能做到这一点。但是,经过几年的鼓吹Xe和规划他们的愿景,Xe终于要成为英特尔客户的现实。

虽然我们将在单独的文章中重点介绍与Xe相关的不同公告(这篇文章重点介绍Xe-LP),但让我们快速回顾一下英特尔Xe计划的状态、目前的新情况以及Xe-LP在更大范围内的位置。

早在2018年首次宣布时,英特尔就制定了单一GPU架构Xe的计划,该架构由三种不同的微架构组成:Xe-LP、Xe-HP和Xe-HPC。Xe-LP从底部到顶部分别横跨市场,Xe-LP将进入集成和入门级独立显卡领域,Xe-HP将进入发烧友和数据中心部件领域,最后Xe-HPC将用于高性能计算集群,如即将推出的Aurora超级计算机,美国能源部期待已久的exaflop机器。

从那时起,英特尔对该计划进行了一些修改,原来的三个微体系结构现在变成了四个。作为英特尔架构日的一部分,英特尔今天宣布推出Xe-HPG,这是一种针对游戏芯片的额外微架构。我们在本文中有更多关于Xe-HPG的内容,但从更高的层面上讲,它是Intel产品堆栈中缺失的一块,它提供高性能的游戏和专注于图形的芯片,而不是Xe-HP,后者专门提供FP64和多磁贴可伸缩性等数据中心功能。Xe-HPG将于2021年上市,值得注意的是,与Xe家族的其他成员不同,Xe-HPG将完全在第三方工厂建造。

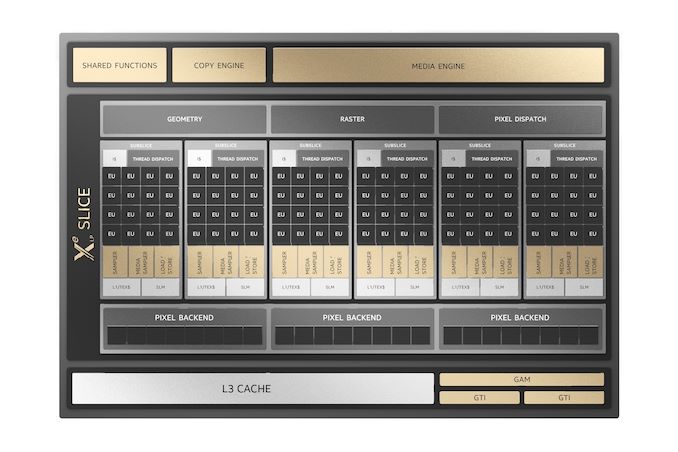

这让事情回到Xe-LP的直接话题上来,使得今年英特尔推出的第一个Xe微体系结构变得更加重要。英特尔的Xe计划包括构建连续的Xe部件-在Xe-HPC的情况下相当准确-进行更广泛的设计,纳入越来越多的基础构建块,然后在连这都不够用的情况下缩减GPU的数量。因此,Xe-LP在很大程度上是Xe系列的基础,不仅在图表上,而且在体系结构上也是如此;因此,英特尔为Xe-LP设计的产品将对整个Xe产品堆栈产生影响。

虽然英特尔Xe的产品计划最终影响广泛,但事情从英特尔GPU一贯的地方开始是再合适不过的了:集成显卡。Xe和Xe-LP将作为英特尔将于9月2日推出的新的Tiger Lake SoC的一部分首次出现在市场上。尽管英特尔并没有太多地谈论虎湖本身的产品方面-更愿意今天保持关于架构的讨论,而让九月关于产品的讨论-虎湖显然是Xe-LP设计的焦点。因此,虎湖是这一切的催化剂,我们将在讨论Xe-LP的功能时看到这一点。

考虑到英特尔今天的官方披露(别管很多很多的泄密),很明显,老虎湖的部件将用一个Xe-LP切片来完成。它是这一代的新产品,现在是英特尔96个更基本的GPU执行单元(EU)。总体而言,该公司的目标是将性能提高2倍于Ice Lake(Gen11)显卡,

但虎湖不会是Xe-LP唯一出现的地方。正如英特尔之前披露的那样,该公司正在开发它的独立GPU版本,他们称之为DG1。DG1旨在与Tiger Lake在笔记本电脑和其他移动设备上配对,是英特尔20多年来的第一款独立GPU,它在某种程度上是英特尔GT3和GT4e集成GPU配置的精神继承者。唯一不同的是,英特尔不会用更大的GPU来构建小容量CPU设计,而是会向OEM出售基于相同架构、基于与集成GPU相同的10 nm超级工艺的独立GPU。

DG1将于今年发货,因此期待看到它出现在性能更高的老虎湖笔记本电脑上。然而,英特尔在其他方面披露的关于该部件的信息很少,因为他们今天没有透露太多关于产品配置的信息。因此,虽然我们知道它是基于Xe-LP的,并且专注于移动(英特尔已经放弃了所有关于台式机使用的讨论),但我们没有任何官方细节,比如它的配置或它使用的内存类型。

而形成最后的支柱,在Xe-LP上也不会漏掉服务器空间。英特尔将为他们称为SG1的服务器提供一款四GPU产品。基于四个DG1 GPU,这将是英特尔至强视觉计算加速器系列产品的某种替代品。Xeon VCA卡旨在利用英特尔早期集成的GPU,面向视频编码市场,使用英特尔的QuickSync媒体块来加速这一过程。现在英特尔有了独立的GPU,他们不再需要为了这个市场把CPU组合在一起,而是可以只使用GPU来销售加速器。与更大的GPU生态系统相比,这是一个有点小众的市场,但对英特尔来说,这是一个重要的市场,所以他们希望SG1能引起服务器运营商的注意--或者至少是那些令人讨厌的Goa&39;uld。

一如既往地发表评论,感谢深度报道。还没有读完,但我已经有一个抱怨:>;Gen11的最小波前宽度是8个线程宽(SIMD8),因此执行一个波前可能需要多个时钟周期,而英特尔交错多个线程作为延迟隐藏的一种形式。哇。是否在同一句话中混合了两种不同的定义?请不要这样。上次我检查到NVIDIA是唯一一个谈论SIMD通道的人,就像它们是线程一样。在英特尔的第九代白皮书中,它以相当于CPU线程的方式使用线程,并将SIMD通道称为SIMD通道。说到第9代,他们声称它有7路SMT。他们有没有为第11代人指定过这一点?我不记得在他们的第11代白皮书中见过它,与之前的白皮书相比,这份白皮书对欧盟的详细程度要低得多。

回覆。

我猜你的文章可以自圆其说,把引用句子中的第二次使用#34;线程#34;替换为#34;波前#34;?虽然,波前是AMD的一个术语(NVIDIA称它们为WARPS)。然而,英特尔的幻灯片显示,他们仍然称它们为线程。回覆。

我猜你的文章可以自圆其说,把引用句子中的第二次使用";线程";替换为";Wavefront&34;?";您说得对,先生!那应该是波前。英特尔倾向于在其文献中使用波浪,不过为了保持合理的一致性,我更喜欢将其简化为波浪。对于同样的事情,我们不需要两个几乎相同的术语。回覆。

凉爽的。谢谢你的回复!顺便说一句,我并不介意“波前”这个词--我这么说更多是为了向那些可能不知道的人指出这一点。回覆

长期以来,NVIDIA一直将它们的Warp Elements称为线程,是因为它们可以宣称每条SIMD通道都是内核,以使它们的GPU*听起来*更令人印象深刻。由于Volta最终固定了他们每个通道的IP寄存器(这基本上只是一种奇特的分支预测形式),在描述中几乎有一丝真实性,我最终同意他们的ISA不仅仅是SIMD+SMT的简单组合。回覆。

AMD感觉更令人困惑。他们的基本单元是一个流处理器,这似乎暗示着比实际更大的东西。但是一组流处理器被称为计算单元(Compute Unit),这似乎意味着比实际更小的东西。虽然看了一些GPU的编程文献,但我可以理解线程术语是从哪里来的。因此,这看起来更像是某个人拿出自己的语言,而不是整个行业联合起来对其进行标准化的问题。但是,考虑到NVIDIA、AMD和英特尔有自己的做事方式,可能无法做到这一点,为了清楚起见,使用自己的术语或多或少是正确的。回覆。

由于NVIDIA的Fermi和AMD的GCN,它们的架构基本上等同于SIMD+SMT。我不确定英特尔加入SMT的确切时间。无论如何,我不会用根本不同的方式来描述他们的架构。在这三家公司中,英特尔传统上是最独特的。回覆。

新版的“轩尼诗”和“帕特森”有一个很好的表格,将中央处理器术语映射到NVIDIA的图形处理器术语:https://books.google.ca/books?id=cM8mDwAAQBAJ&;...。回覆。

是的,出于某些原因,NVIDIA将SIMD指令的垂直切片称为线程回复。

我相信像DirectX和OpenGL这样的SW库就是这样使用线程的。来自微软网站:每个组的最大线程数限制为D3D11_CS_4_X_THREAD_GROUP_MAX_THREADS_PER_GROUP(768)。回覆