惠普纳米处理器第二部分:从掩模到电路的逆向工程

1974年,惠普开发了一种微处理器,用于他们产品中的控制应用,从软盘驱动器到电压表。这个简单的处理器是典型微处理器的一个缩影-它甚至不支持加减1-所以被称为纳米处理器。纳米处理器的主要特点是它的低成本和高速:与当代的摩托罗拉6800相比,纳米处理器的价格是15美元,而不是360美元,执行控制任务的速度要快几个数量级。

几十年来,这个处理器一直默默无闻,直到它的设计者拉里·鲍尔最近将芯片的掩模和文档捐赠给CPU Shack,CPU Shack扫描了掩模,并撰写了关于纳米处理器的文章。在Antoine Bercovici将图像缝合在一起后,2i基于它们写了一篇纳米处理器概述文章。这篇博客文章是第二部分,在那里我将详细讨论一些纳米处理器电路,从面具对其进行反向工程。这些功能块值得研究,因为纳米处理器将其实现精简到最低,同时仍然是一个有用的微处理器。这篇博客文章是第二部分,我在那里详细讨论了一些纳米处理器电路,从面具对其进行反向工程。这些功能块值得研究,因为纳米处理器将其实现精简到最低,同时仍然是一个有用的微处理器。

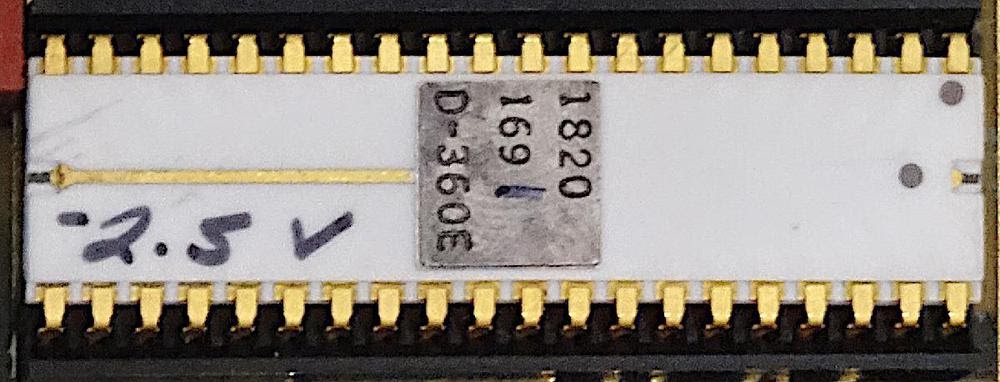

惠普纳米处理器,部件号1820-1691。请注意手写偏置电压";-2.5V";,它随芯片的不同而不同。零件号的最后一个数字(1)也是手写的,表示芯片的速度。照片由Marc Verdiell提供。

像那个时代的大多数处理器一样,纳米处理器是一个8位处理器,但是它不支持RAM,3而是从外部2千字节的ROM运行代码。它包含16个8位寄存器,比大多数处理器都多,足以弥补许多应用中RAM的不足。纳米处理器有48条指令,指令集比摩托罗拉的72条指令小得多。但是,纳米处理器包括方便的位设置、清除和测试操作,这是那个时代的其他处理器所缺乏的。它还有多个I/O指令,既支持I/O端口,也支持通用I/O引脚,使得使用纳米处理器控制设备变得容易。

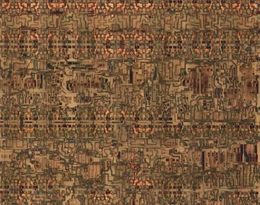

来自纳米处理器的组合面具。单击查看大图。文件由Antoine Bercovici提供,使用CPU Shack的扫描。

上面的掩模图像显示了纳米处理器的简单性,蓝色线条表示芯片顶部的金属布线,绿色线条表示芯片下面的硅。外面的黑色方块是40个焊盘,用于连接IC的外部引脚。芯片内部的黑色小区域是晶体管;如果你眯着眼睛,你应该能数出4639个。4.。

下面的框图显示了纳米处理器的内部结构。16个存储寄存器位于中间。比较器允许比较条件分支的两个值。控制逻辑单元在累加器上执行递增、递减、移位和位操作,缺少标准算术/逻辑单元(ALU)的算术和逻辑操作。程序计数器(右)将指令取到指令寄存器(左);中断和子例程调用中的每一个都有一个返回地址的单项堆栈。

我要强调的是,尽管纳米处理器很简单,也没有算术运算,但它不是一个仅仅切换一些控制线的玩具处理器,而是一个用于复杂任务的快速且功能强大的处理器。例如,惠普98035实时时钟模块使用纳米处理器来解析24个不同的ASCII命令字符串,以及计算每个月的天数等活动。

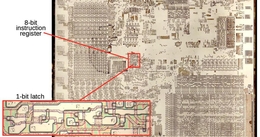

下面的芯片照片显示,纳米处理器的大部分芯片被它的16个寄存器占据。这些寄存器通过数据总线与芯片的其余部分通信。寄存器上方的电路选择特定的寄存器,右侧的寄存器R0紧挨着比较器,稍后将重点介绍。

寄存器占据了纳米处理器芯片的很大一部分。下面的芯片照片由Pauli Rautakorpi拍摄,抄送3.0。

寄存器的构建块是反馈环路中的两个反相器,存储单个位,如下所示。如果顶线为0,则右侧反相器将向底线输出1。然后,左边的逆变器将输出0到顶线,完成周期。因此,电路是稳定的,并且将记住0。同样,如果顶部焊线为1,则底部焊线将反转为0,顶部将反转为1。因此,该电路可以存储0或1,从而形成1位存储器。

下图显示了这种双反相器存储是如何在芯片上实现的。左边显示了掩模图像的物理布局。布局进行了优化,使单元尽可能小。蓝色线条表示金属层,绿色线条表示硅层。中间的示意图显示了相应的晶体管电路。每个逆变器由一对晶体管组成,如右图所示。顶部和底部的晶体管都是直通晶体管,可以访问存储单元。

纳米处理器中的一位存储空间。每个位由6个晶体管(也称为6T SRAM单元)实现。

寄存器组由这些位单元的矩阵构成。寄存器选择线选择一个寄存器(一列)用于读取或写入。当被选择时,顶部和底部通过晶体管将反相器连接到相应的水平位线。对于读取操作,顶部位线提供存储在单元中的值;对于寄存器中的8位,有8对位线。对于写入操作,将该值施加到上部位线,将反相值施加到下位线。这些值超过来自反相器的信号,迫使反相器达到所需的值并存储位。因此,水平位线和垂直选择线的栅格允许读取或写入特定的寄存器。

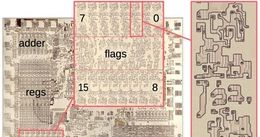

指令解码电路负责获取二进制指令码(例如01101010)并确定它是什么指令(在这种情况下是从寄存器10"加载累加器)。的指令非常简单:指令相对较少(48条),操作码始终为1字节长。下图显示指令解码逻辑(红色)占据了芯片的很大一部分。指令寄存器(绿色)是保存当前指令的一组8个锁存器。指令寄存器紧挨着提供来自ROM的指令的数据引脚。本节将重点介绍黄色方框中的解码电路。

芯片的很大一部分用于指令解码(RED)。本节将重点介绍以黄色突出显示的电路。下层模具照片:Pauli Rautakorpi,抄送3.0。

译码由NOR门完成;每个NOR门检测特定的指令或指令组。NOR门接受指令位或它们的补码作为输入。当所有输入均为零时,NOR门指示匹配。这允许针对整个指令或部分指令进行匹配。例如,从寄存器R";加载累加器指令的二进制格式为";0110rrrr";,其中最后四位表示所需的寄存器。NOR门(bit7+bit6';+bit5';+bit4)';将匹配该形式的指令。

以这种方式构造指令解码器的好处是,它可以由紧凑、规则的电路(通常称为PLA)构建。6其想法是使输入信号水平运行而垂直输出的矩阵。每个交叉点可以有一个晶体管,使输入信号成为门的一部分;或者没有晶体管,忽略该输入信号。结果是紧密堆积的或非门。

右下图放大了上面以黄色突出显示的三个解码器。原理图对应于最左边的解码器;请注意原理图中晶体管与布局中粉红色晶体管之间的对应关系。其思想是,如果任何输入给晶体管通电,则晶体管将把输出拉到地面。否则,输出被电阻器拉高。底部的逆变器放大信号,提供足够的电流来驱动累加器的所有八个片。7奇怪的是,布局使用成对的晶体管,都连接在接地和输出之间;我看不出与使用单个晶体管的直接方法相比有什么优势。无论如何,请注意PLA式矩阵是如何为解码器提供密集布局的。

这张图显示了纳米处理器中的一个解码器电路。该示意图对应于右侧显示的三个解码器中最左边的解码器。

该特定电路产生馈送到累加器电路的递增/递减信号。该电路在时钟、提取、指令位6和指令位2都为低时匹配,因此它在执行阶段匹配x0xx0xx形式的指令。这些指令包括";递增二进制";(00000000),";递增bcd";(00000010),";递减二进制";(00000001)和";递减bcd";(00000011),这些指令包括";递增二进制";(00000010),";递减二进制";(00000001)和";递减bcd";(00000011)。8个。

纳米处理器中的一个重要电路是比较器,它确定累加器A是大于、小于还是等于寄存器R0。比较器使用一个简单但巧妙的电路来比较这两个值。算法本质上是比较从最高有效位开始的两个数字。只要位相等,就继续移到较低有效位。两个数字之间的第一个差异确定哪个更大。(例如,对于10101010和10100111,突出显示的位确定第一个数字更大。)。

该算法由8个阶段实现,每个阶段每位一个,从底部最高有效位开始。每个阶段(下图)由两个对称部分组成:一个阶段确定A&>R0是否相等,而互补阶段确定A<;R0是否相同。如果到目前为止数字相等,但这两个位在这一阶段不同,则该阶段产生大于或小于信号。否则,它传递较低阶段的判决。最上面的阶段输出最终判决。注意,比较器为自由提供相等测试#34;;如果输出为#39;;则#34;;如果输出为#39;#34;;则该阶段产生大于或小于的信号,否则传递较低阶段的判决。注意,比较器提供相等测试#34;用于自由测试#34;;如果输出为#39;#34;;则产生大于或小于的信号。T大于或小于时,这两个数字相等。

下图显示了两个比较器阶段的物理布局。比较器布局的一个巧妙特点是,它位于左侧的寄存器0和右侧的累加器之间,最大限度地减少了布线。比较器直接访问寄存器0,而不通过寄存器选择和数据总线的常规路径。

纳米处理器的条件分支指令可以测试比较器输出。9分支电路相当简单:分支指令的几位通过乘法选择特定的测试。然后,指令的位7选择分支,如果为真,则选择分支;如果为假,则选择分支。与大多数处理器不同,纳米处理器不选择。不提供到任意地址的分支。取而代之的是,如果条件满足,它跳过两个指令字节。(通常这两个字节将保持到所需目标的跳转,但有时保持其他指令。)跳过电路很简单:程序计数器递增器(如下所述)被第二次触发,但是递增2而不是1,跳过两条指令。因此,纳米处理器用相对较少的电路实现了一组广泛的条件测试。

累加器是存储当前正在处理的字节的特殊8位寄存器。对累加器的操作是由控制逻辑单元(CLU)执行的,手册称之为纳米处理器的核心。CLU等同于大多数处理器中的算术/逻辑单元(ALU),只是它不执行算术或逻辑操作。不过,CLU并不像它听起来那样无用。它可以用二进制和二进制编码的十进制(BCD)递增或递减累加器。(二进制编码的十进制每个字节存储两个十进制数字。这对于十进制I/O或显示器非常有用。)CLU还可以补充或清除累加器,或者设置或清除特定位。最后,它支持左移位和右移位操作。

上图显示了累加器和CLU的布局。第一个区域有各种电路来检测零值;例如,通过检测9位来支持BCD;并提供从低4位开始的快速进位生成。我不会详细讨论这一点,但请注意该电路的不规则布局。第二个区域保存主累加器和CLU电路;我将在下面详细讨论这一点。第三个区域将控制信号从上面的解码逻辑分配到八个累加器切片。最后,最后一个区域保存指令解码逻辑,以解码位操作并向相应的累加器切片发送信号。(注:第二个区域保存主累加器和CLU电路;下面将详细讨论此问题。第三个区域将控制信号从上面的解码逻辑分配到八个累加器切片。最后,最后一个区域保存指令解码逻辑,以解码位操作并向相应的累加器切片发送信号。

累加器/CLU的主要部分由8个片组成,每个片对应一个片,最低的位在顶部。我将讨论每个片中的四个电路:递增/递减器的进位生成、递增/递减器的位生成、选择新的累加器值的多路复用器以及保存累加器的值的锁存器。

递增/递减电路的方向取决于操作码:操作码的低位中的0表示递增,而操作码中的1表示递增。下面左边的进位电路产生进位输出信号。对于增量,如果存在进位输入并且当前位是1(因为它将递增到二进制10),则存在进位输出。对于递减,进位线指示借用,而不是进位,因此如果存在进位输入(即,借用)并且当前位为0,则存在进位输出,从而触发借用。

右边的电路在递增或递减时更新当前位。如果有进位输入,则当前位翻转,本质上是由三个或非门实现的异或。一个复杂的问题是对BCD(二进制编码十进制)的调整。对于BCD递增操作,进位在递增9位时发生,而对于BCD递减,0位递减到9,而不是递减到二进制1111。

不同的累加器操作由下面的多路复用器提供。根据操作情况,将激活一个通过晶体管,选择所需的值。例如,对于递增/递减操作,顶部晶体管选择来自上述递增/递减电路的输出。该晶体管由前面描述的与递增/递减指令匹配的指令解码器激活。类似地,右移指令激活右移通过晶体管,将累加器位n+1馈送到每个累加器片以移位值。

保持累加器一位的锁存器示意图,以及选择累加器输入的多路复用器。

上面的锁存器存储累加器的一位。当保持累加器晶体管被激活时,两个NOR门形成一个保持值的环路。但是当加载累加器晶体管被激活时,累加器从乘法器加载其值。清除位n和设置位n线允许指令修改累加器的各个位;相比之下,多路复用器一次更新所有累加器位。

另一个很大的电路块是位于纳米处理器左下角的11位程序计数器,我将对其进行简要描述,该块还包括一个锁存器和第二个锁存器,锁存器用于保存子例程调用的返回地址,第二个锁存器用于在中断后保存程序计数器。(您可以将其视为单条目堆栈。)程序计数器包括一个递增器,用于将其前进到下一条指令。该递增器还可以递增两条,允许条件分支指令跳过两条指令。(递增二是通过递增位1而不是位0来实现的。)为了提高递增器的性能,它具有跳过进位功能;如果最下面的六位都是1,则它将立即递增位6,而无需等待进位通过低位传播。

纳米处理器的最后一部分是控制电路。与其他微处理器相比,纳米处理器的控制电路几乎微不足道:处理器在取回和执行周期之间交替(偶尔会中断)。控制电路只不过是几个触发器和门,所以我不会再多说了。

下面的图表总结了纳米处理器的主要功能模块,纳米处理器实现了这些模块的密集布局,比我预期的过时的金属栅极技术要好得多。逆向工程表明,这些功能块是用简单但精心设计的电路实现的。

惠普纳米处理器的功能组件,基于我的逆向工程。下面的芯片照片由Pauli Rautakorpi拍摄,CC by 3.0。

纳米处理器是一种不同寻常的处理器。我的第一印象是它甚至不是一个真正的处理器,因为它缺乏基本的算术功能。但是,在研究了它之后,我印象更深。它简单的设计使它的运行速度比当时的其他处理器更快。指令集比最初看起来更有能力。惠普在20世纪70年代和80年代的许多产品中都使用了纳米处理器,扮演的角色比你复杂得多。在20世纪70年代和80年代,惠普(Hewlett-Packard)在许多产品中使用了纳米处理器,所扮演的角色比你更复杂。在20世纪70年代和80年代,惠普(Hewlett-Packard)在许多产品中使用了纳米处理器,扮演的角色比你复杂得多。现在,有了CPU Shack发布的掩模,我们可以了解使纳米处理器工作的电路的秘密。

纳米处理器(白色芯片),作为HP时钟模块的一部分。请注意芯片上的手写电压;每个芯片需要不同的偏置电压。图片由Marc Verdiell提供。

在Twitter上关注我的博客帖子@kenshiriff。我还有一个RSS订阅。感谢Antoine Bercovici扫描并重新制作面具,Larry Bower捐赠,以及CPU Shack的John Culver分享捐赠。

虽然没有加法指令,但纳米处理器可以通过重复的递增和递减操作(它支持)来(缓慢地)加数字。(惠普实时时钟模块的代码做到了这一点。)其他应用程序,如HP电压表,添加了外部算术逻辑单元芯片(74LS181)来执行快速加法;这些都是被访问的ASI/O设备。(当然,在图灵完备性的情况下,纳米处理器理论上可以做任何事情,从浮点函数到密码运算;它只是非常慢。)-↩。

纳米处理器没有支持RAM的指令,因为它是为通常不需要太多存储的控制应用程序设计的。然而,一些纳米处理器应用程序使用随机存取存储器,将随机存取存储器视为I/O设备。地址被写入一个I/O端口,数据字节从另一个端口读取或写入。-↩。

根据我的统计,纳米处理器有4639个晶体管。由于布局原因,指令解码器由成对的小晶体管构成;将这些对组合在一起产生3829个独特的晶体管。其中,1061个是引体向上,2668个是活动的。相比之下,6502有4,237个晶体管,其中有3,218个活跃.8008有3,500个晶体管,摩托罗拉6800有4,100个晶体管.--↩。

制作一个fpga版本的纳米处理器可能会是一个有趣的项目,因为纳米处理器就像你能做一个真正的商业处理器一样简单。《用户指南》解释了这些指令,并提供了可以执行的示例代码。-↩。

从NOR门阵列中构建解码器解码在EA中很常见。

.