IBM创建了世界上第2个NM芯片

周四,IBM宣布在集成电路设计中突破 - 世界' S前2纳米工艺。 IBM表示,它的新过程可以生产能够高出表现更高的45%,或比现代7 NM设计更高的能源使用较低的75%。

如果你'近期的处理器新闻,你&#39其竞争对手在更小的过程中,最小的生产芯片是Apple'在5 nm的新M1处理器。什么'不太清楚的是第一名意味着什么。

最初,工艺尺寸引用晶片本身上晶体管的文字二维尺寸 - 但现代3D芯片制造过程已经成为散列。铸造厂仍然指的是纳米的过程大小,但它' s a" 2d等价度量"只松散地耦合到现实,其真正的意义从一个制造商到下一个制造商变化。

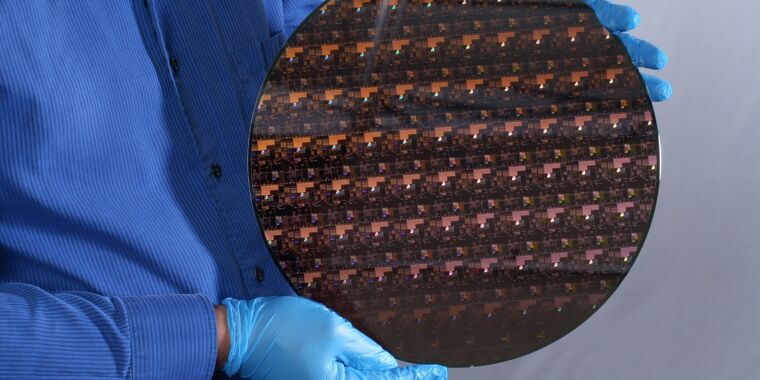

为了更好地了解IBM' S新的2nm流程堆叠,我们可以看一下晶体管密度 - 通过从Wikichip和IBM&#39的信息采购的生产过程信息。 S博士IAN CHERRESS,谁让IBM翻译"指甲&#34的大小; - 用新的过程用新的工艺包装50亿晶体管 - 进入150平方米。

正如您在上图中看到的那样,简单"纳米"度量标准从一个铸造铸造到另一个铸造,英特尔' S流程比&#34所暗示的晶体管密度更高的晶体管。度量标准,其10 nm柳树cove cpus大致与来自tsmc' s代ries的7个nm零件。 (TSMC为AMD,Apple和其他高调客户构建处理器。)

虽然IBM声称新过程可以"四重手机电池寿命,只需要用户每四天充电他们的设备,"它仍然太早归因于在新工艺上设计的筹码混凝土电力和性能特征。将晶体管密度与现有过程相比也似乎从IBM'帆船上的一些风 - 比较新的设计到TSMC 7 NM是良好的,但TSMC' S 5 NM进程已经在生产中,并且它的3 nm工艺 - 具有非常相似的晶体管密度 - 明年的生产状态是在轨道上。

我们在新过程中没有任何现代产品的现实产品公告。但是,IBM目前与三星和英特尔一起工作伙伴关系,他们可能会将这个过程融入自己的未来生产。